コンパイル

C言語で書いたコードを実行するためには

最終的に機械語に変換しないと動作しないのと同様に、

設計した回路も、FPGA内の論理ブロックの

構成情報に変換しないとFPGA上では動作しません。

この作業は、C言語の時と同様にコンパイルと呼びます。

厳密には、以下の3段階に分かれますが、

あまり気にする必要はないと思います。

- 回路図をRegister Transfer Levelという表記に変換する。

RTLはGCCの中間言語と考えてもらえば良いでしょう。

- RTLで記述された回路をFPGA上の論理ブロックに割り付け、

論理ブロックの配置や配線を行う。

- 配置/配線の情報をバイナリで記述された構成情報ファイルに変換する。

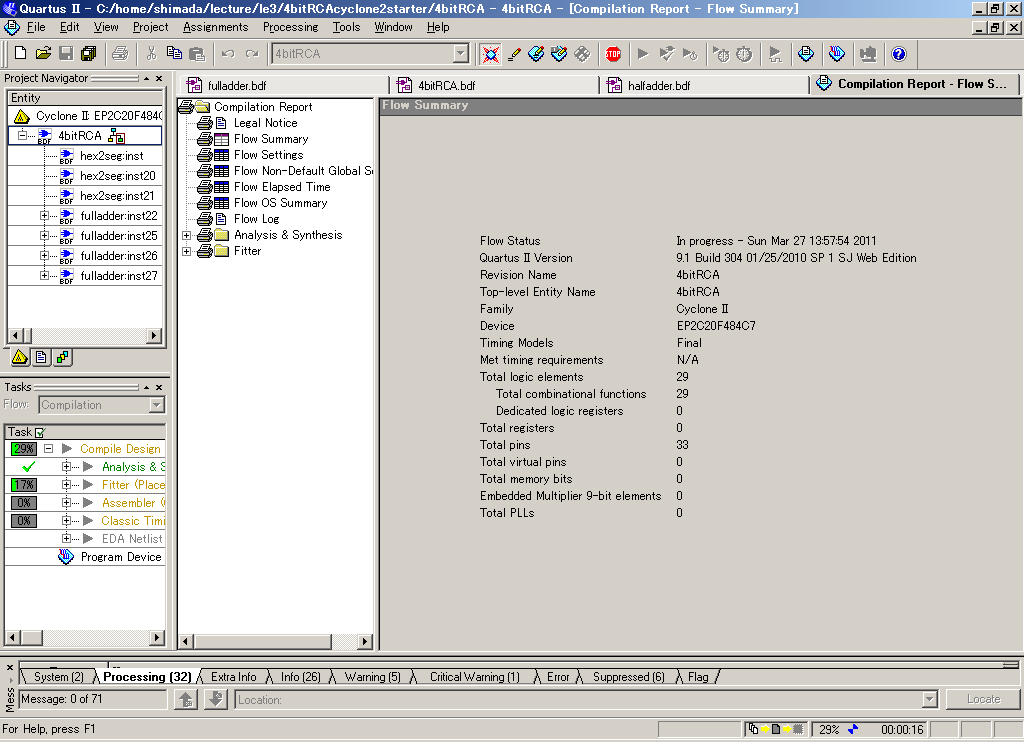

以下はコンパイルの手順です。

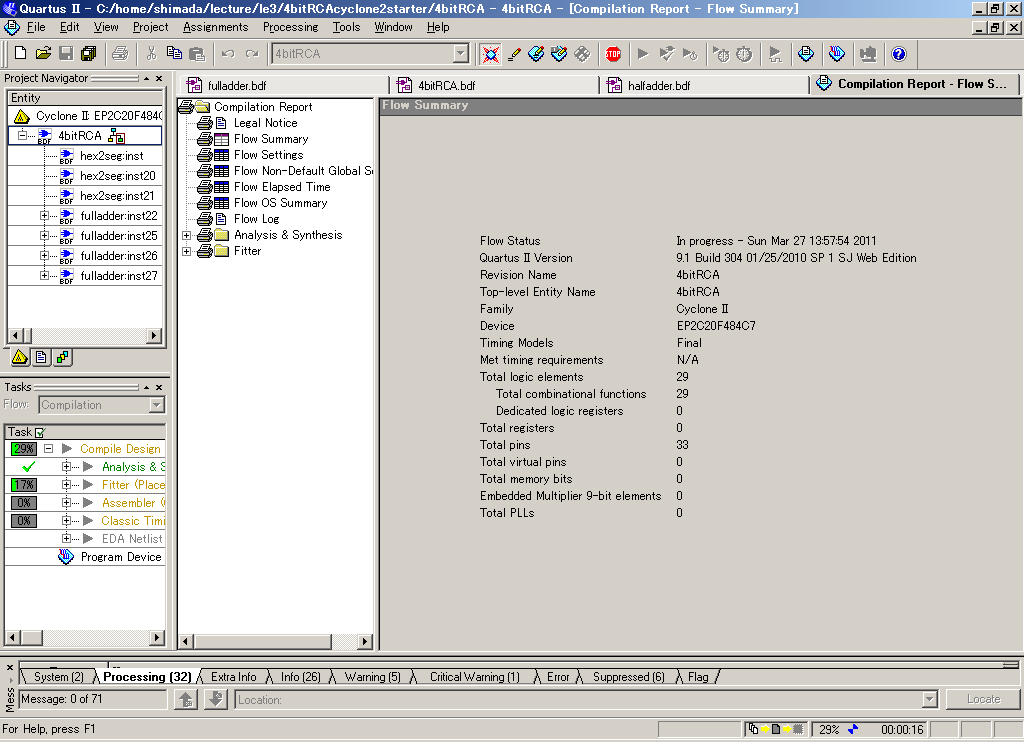

- "Processing→Start Compilation"でコンパイルを実行する。

以下のように左下でコンパイルの進行状況を表示しながら、

コンパイルが進行する。

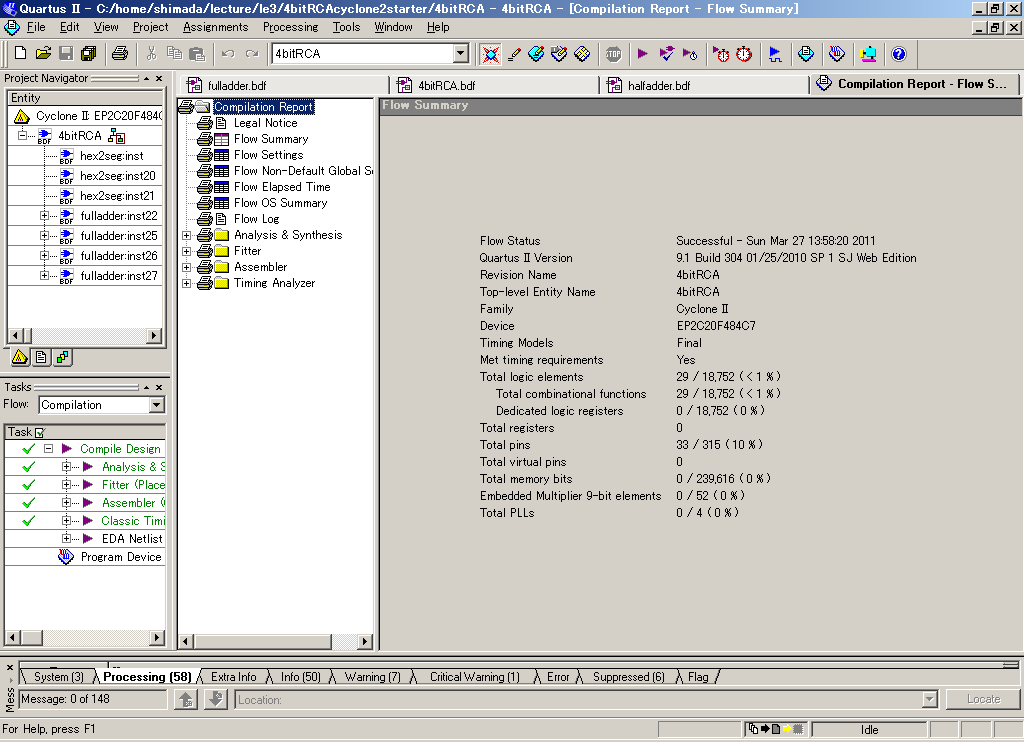

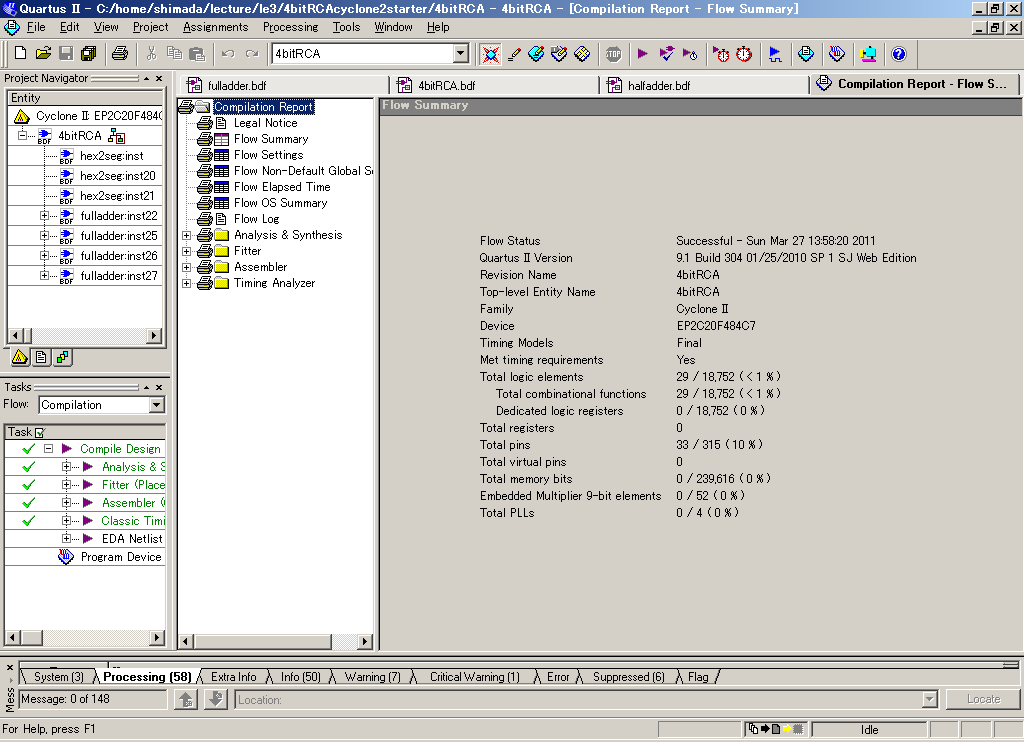

- 正常終了したならば特に問題無し。

コンパイルのレポートが出るので、必要に応じて解析する。

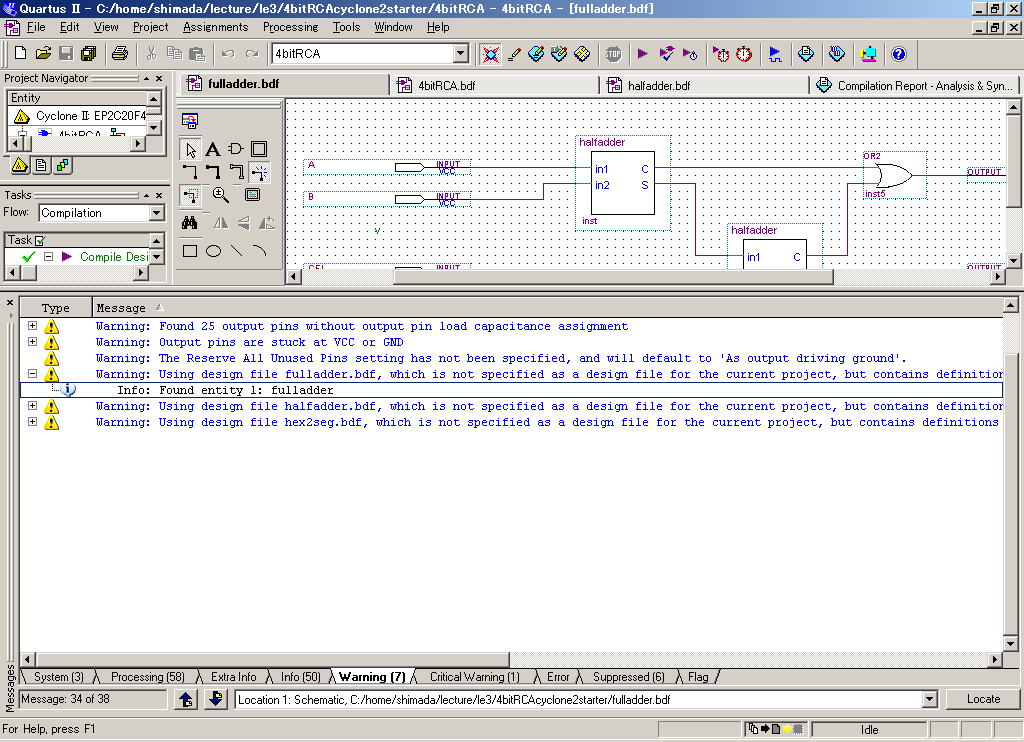

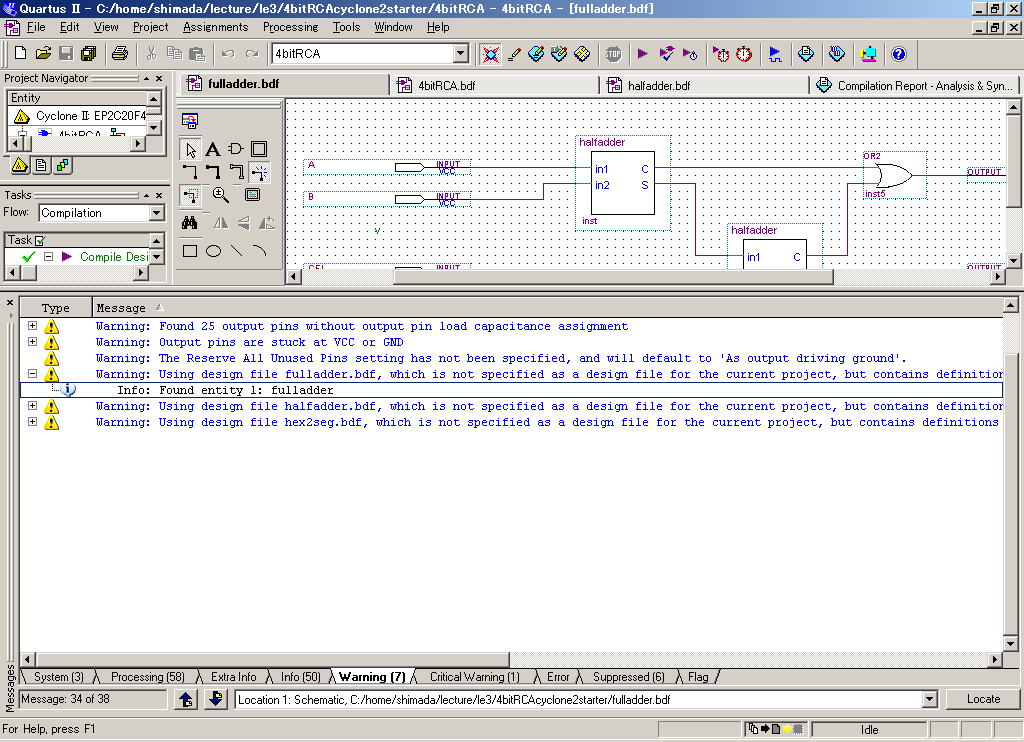

- 正常終了しなかった場合は、

"Compilation Report→Analysis & Synthesis→Messages"で確認する。

(基本的に、自動的にメッセージは下に出てくるようになる。)

- ライブラリから呼び出した論理ゲートや回路ブロックには

インスタンス名がつけられており、回路図エディタ上の

それらの左下にインスタンス名がついています。

- コンパイル時のメッセージに"inst??(デフォルト名)"というのがあれば、

そのインスタンス番号の論理ゲート等の周りをチェックしましょう。

- トップのBlock Diagramのファイル名がプロジェクト作成時に

していたTop-Level Entityと同じでないと、コンパイルがうまくいきません。

この場合、FAQに書かれている方法で対処しましょう。

- コンパイラの出す警告も注意して見ておけば、

設計ミスとかに気づくかもしれません。

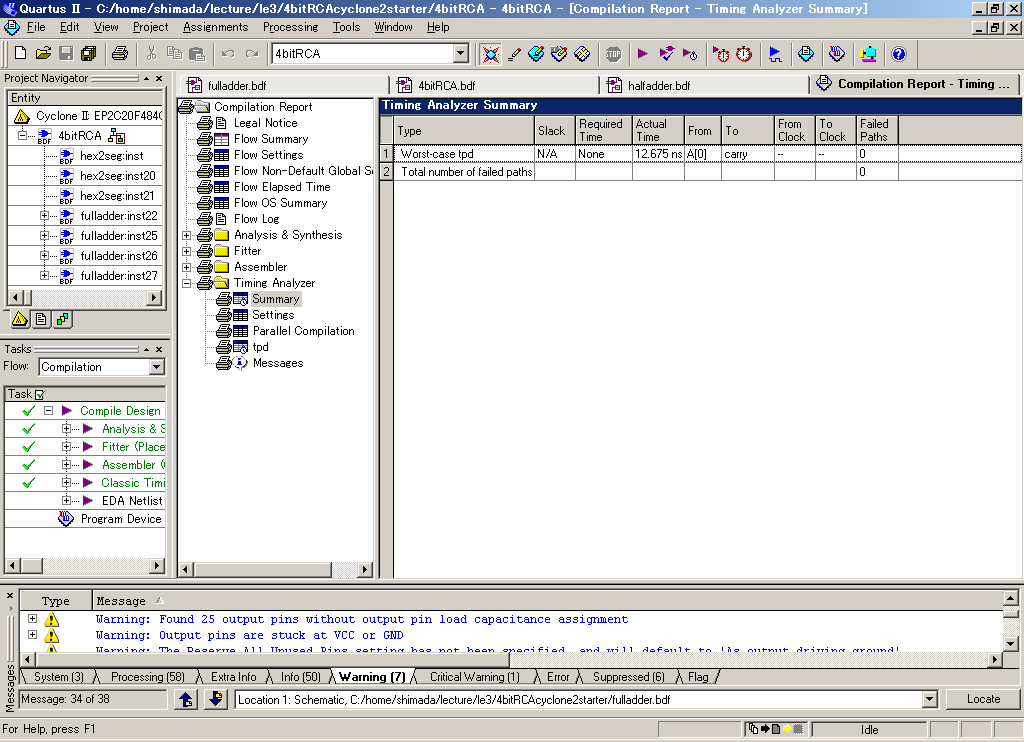

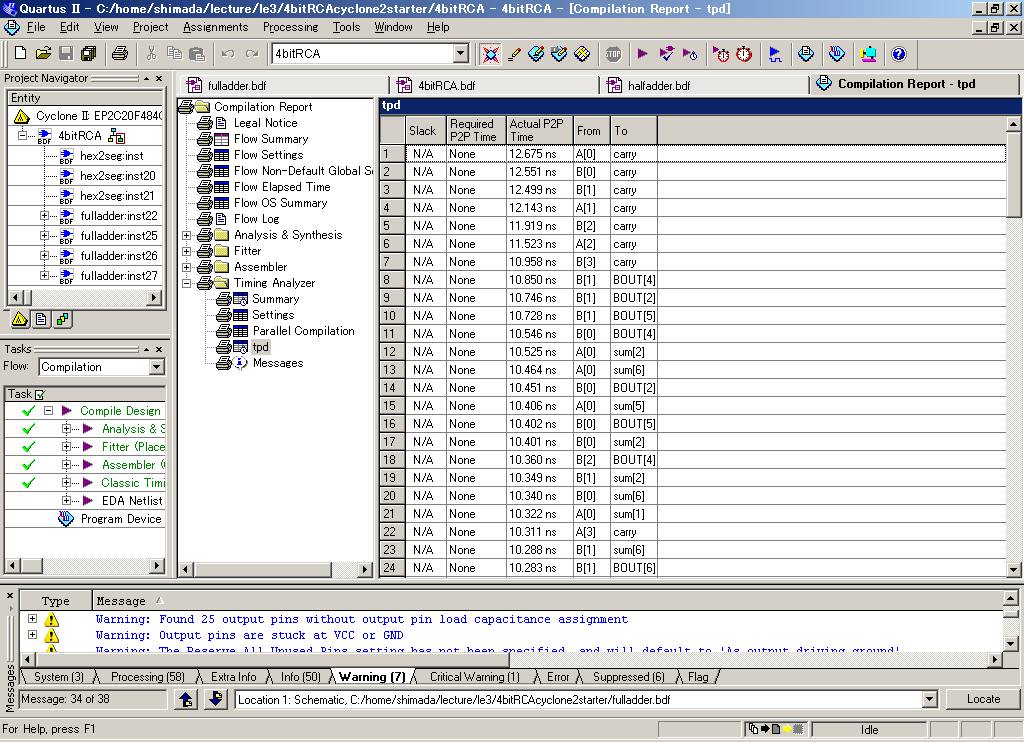

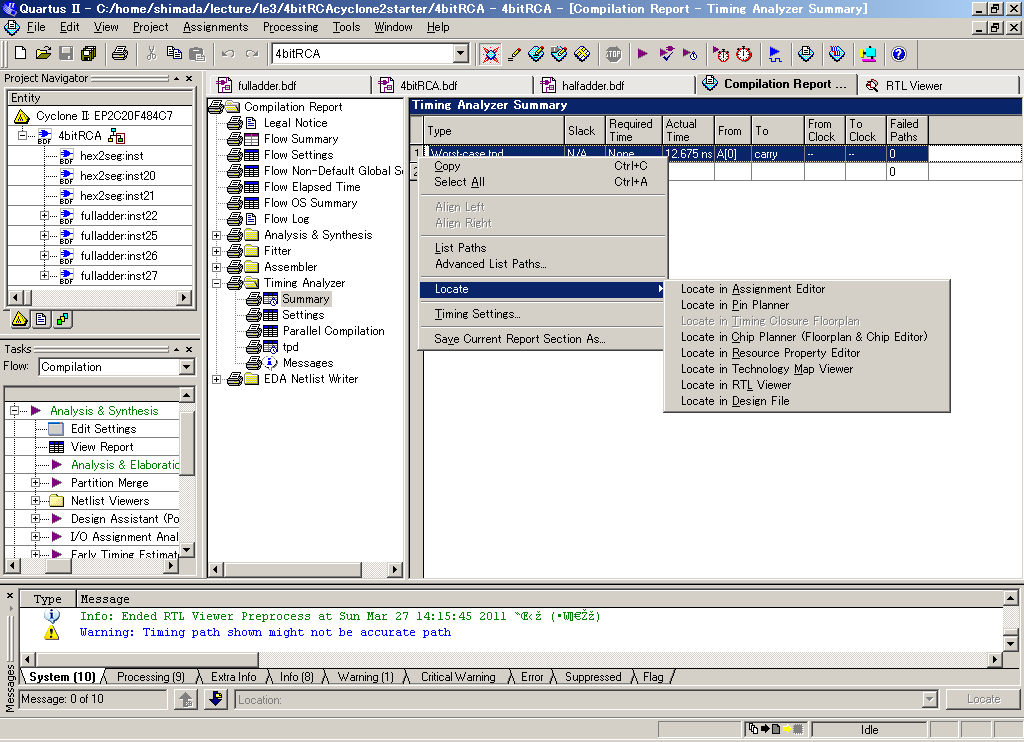

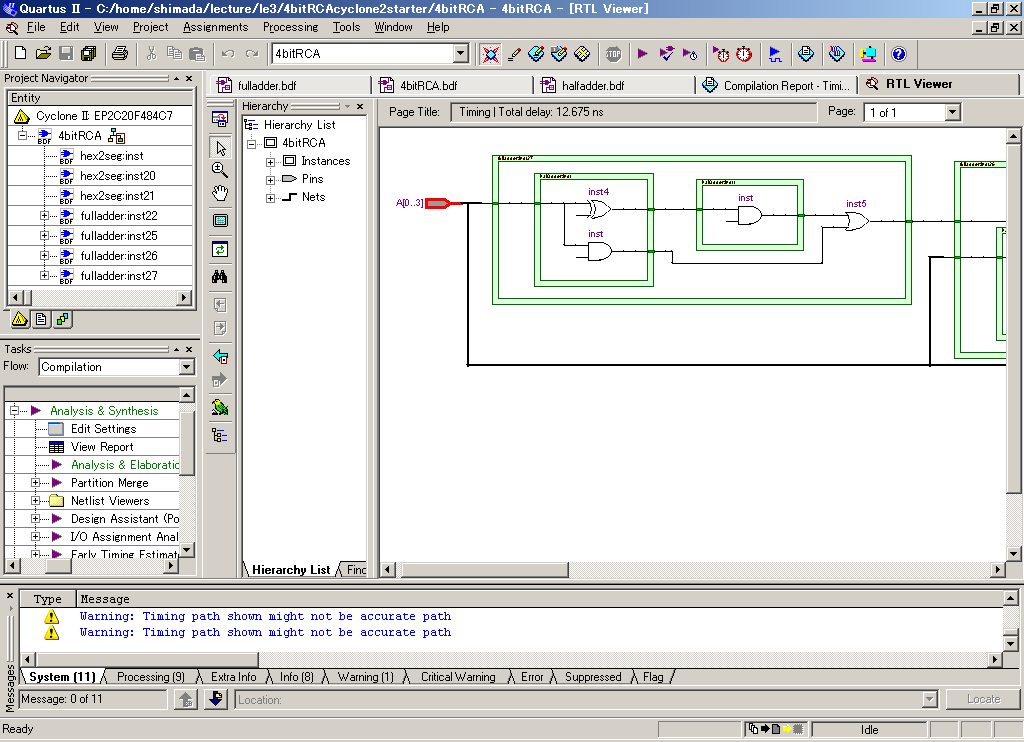

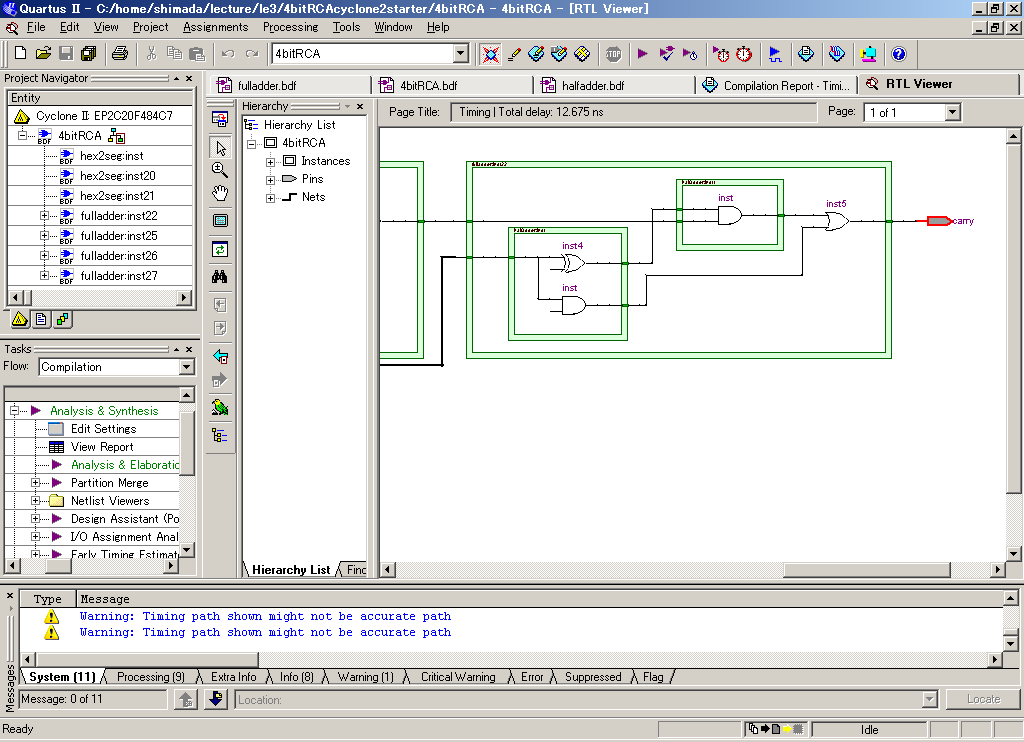

レポートなどの考察に使えそうなCompilation Report

Last modified: 2010/4/7 11:00