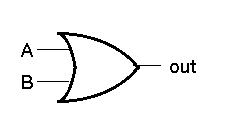

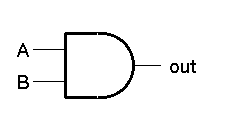

回路記号

真理値表

| A | B | out | |

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

備考

論理積のゲート。入力数が増えたAND3,AND4,...等のバリエーションがある。

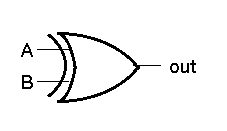

また、出力の真偽が反転した(出力側にNOTがついた)NANDや、

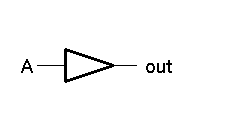

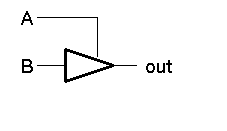

入力の真偽が反転した(入力側にNOTがついた)BANDもある。

ORと組み合せて組み合わせ論理回路の構成によく使われる。

プロセッサの制御部を作った後(デバッグもした後)では、

見るのもいやになるかもしれない・・・。