回路図

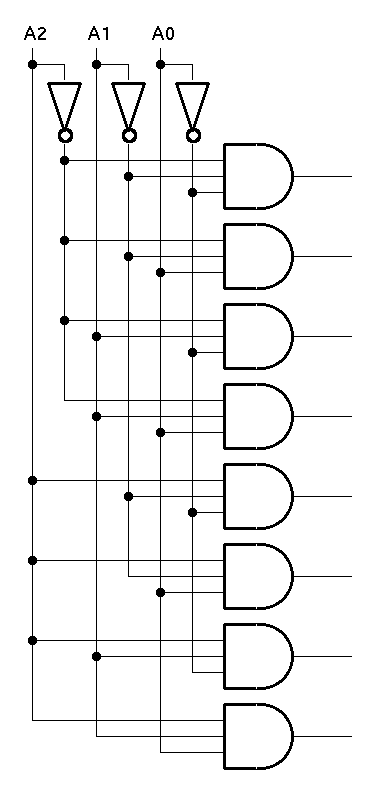

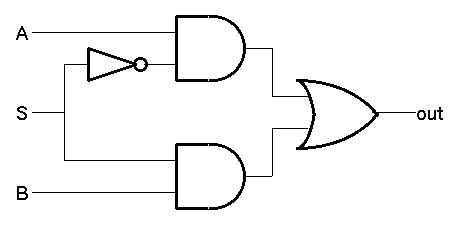

AND-ORによる実現

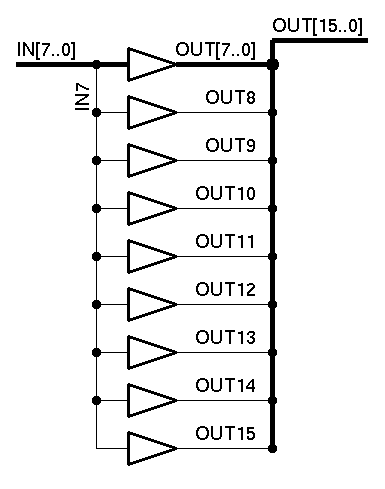

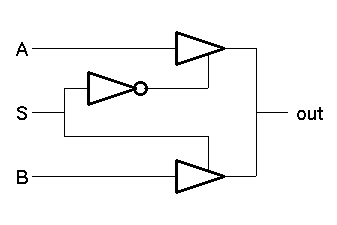

3状態バッファによる実現

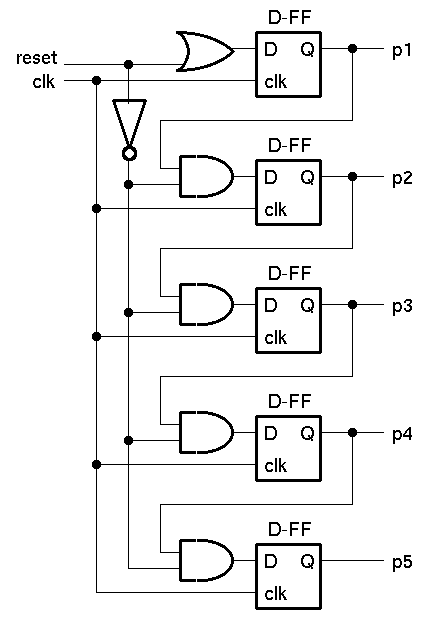

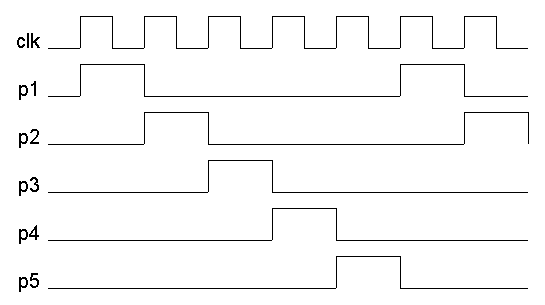

備考

この回路図は、2入力1出力のマルチプレクサであり、

Sの内容に応じて、A,Bのどちらをoutに出力するかを選択する回路である。

この実装では、Sが0の時にAの内容がoutに出力され、

Sが1の時にBの内容がoutに出力される。図にはAND-ORを使った組み合わせ回路と 3状態バッファを使った実現例があるが、 どちらでも容易に3入力1出力,4入力1出力,...に拡張できる。

なお、マルチプレクサとは逆に、1つの信号を 複数の出力のうちの1つに選択的に出力する回路は デマルチプレクサと呼ばれる。 こちらの回路図は、マルチプレクサの構成が理解できていれば すぐに思い付くと思うので、特に記載しない。