ModelSim によるシミュレーション (テストベンチなし)

(参考) Quartus II Ver.9 以前の方法は、

テスト波形ファイルを使ったシミュレーション (Ver.9まで)

を参照。

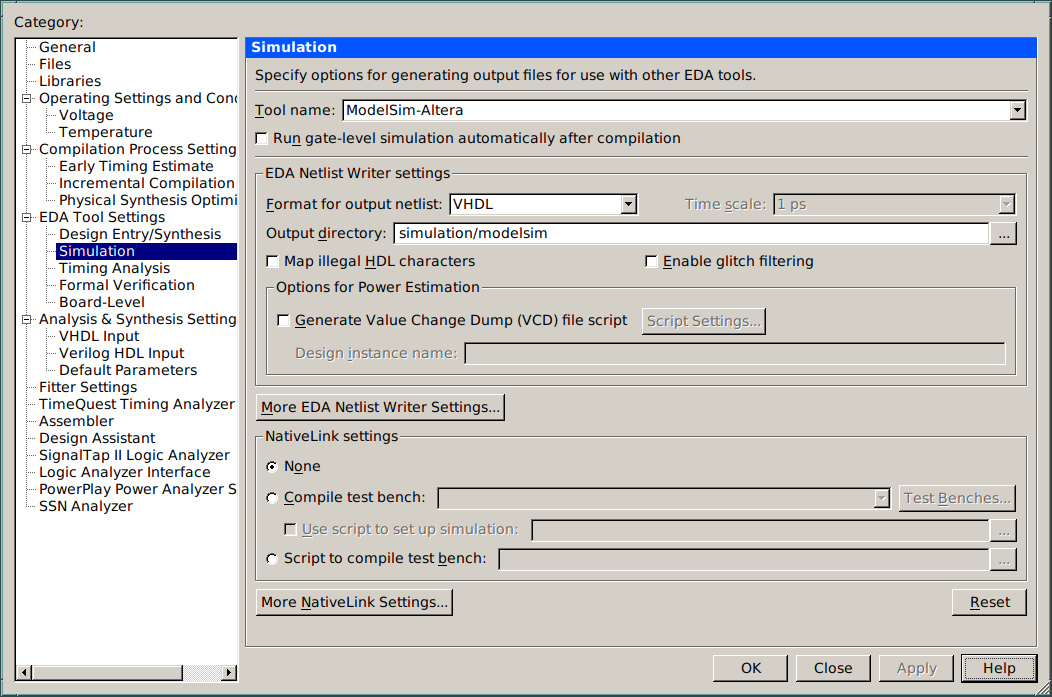

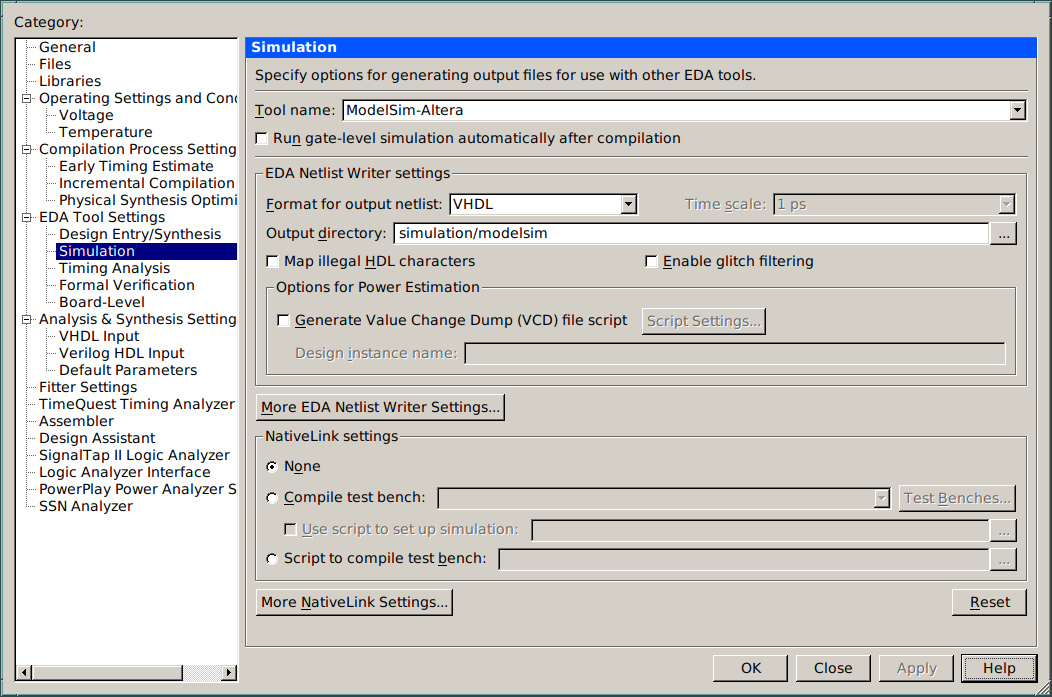

設定

Quartus II からシミュレーションツール ModelSim-Altera を呼び出すための設定をする。

- "assignments" → "settings" で設定ウィンドウを開く。

- "EDA Tool Settings" - "Simulation" カテゴリを開く。

- "Tool name:" で "ModelsSim-Altera" を選択する。

- "Format for output netlist:" で "VHDL" を選択する (Verilog HDL, System Verilog でもたぶん以下同様)。

- "OK"

- "Tools" → "Options.." でオプション設定ウィンドウを開く。

- "EDA Tool Options" タブを開く。

- "ModelSim-Altera" の場所が設定されていなければ、"/opt/altera/13.0sp1/modelsim_ae/bin" に設定する。

合成

Quartus II で回路をコンパイルし、"Compilation Report" の "EDA Netlist Writer" の下の Summary, Settings, Generated Files を確認する。

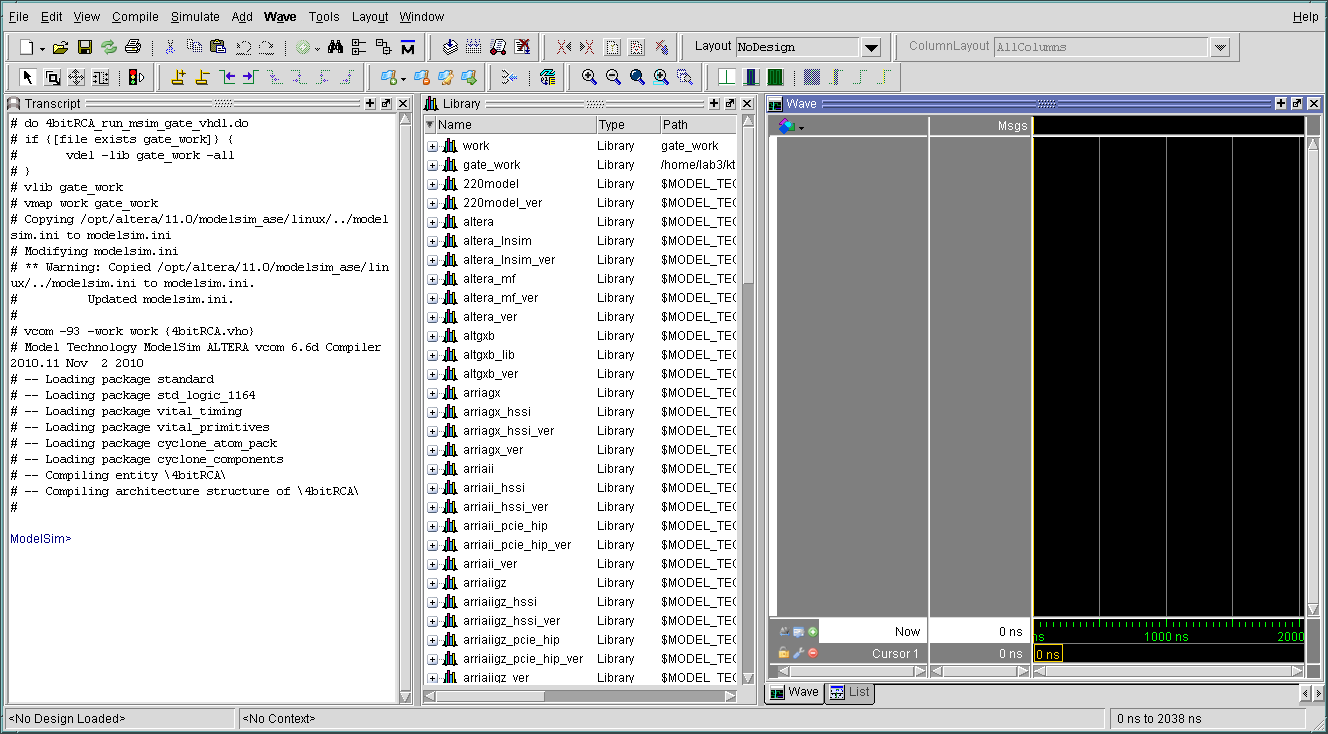

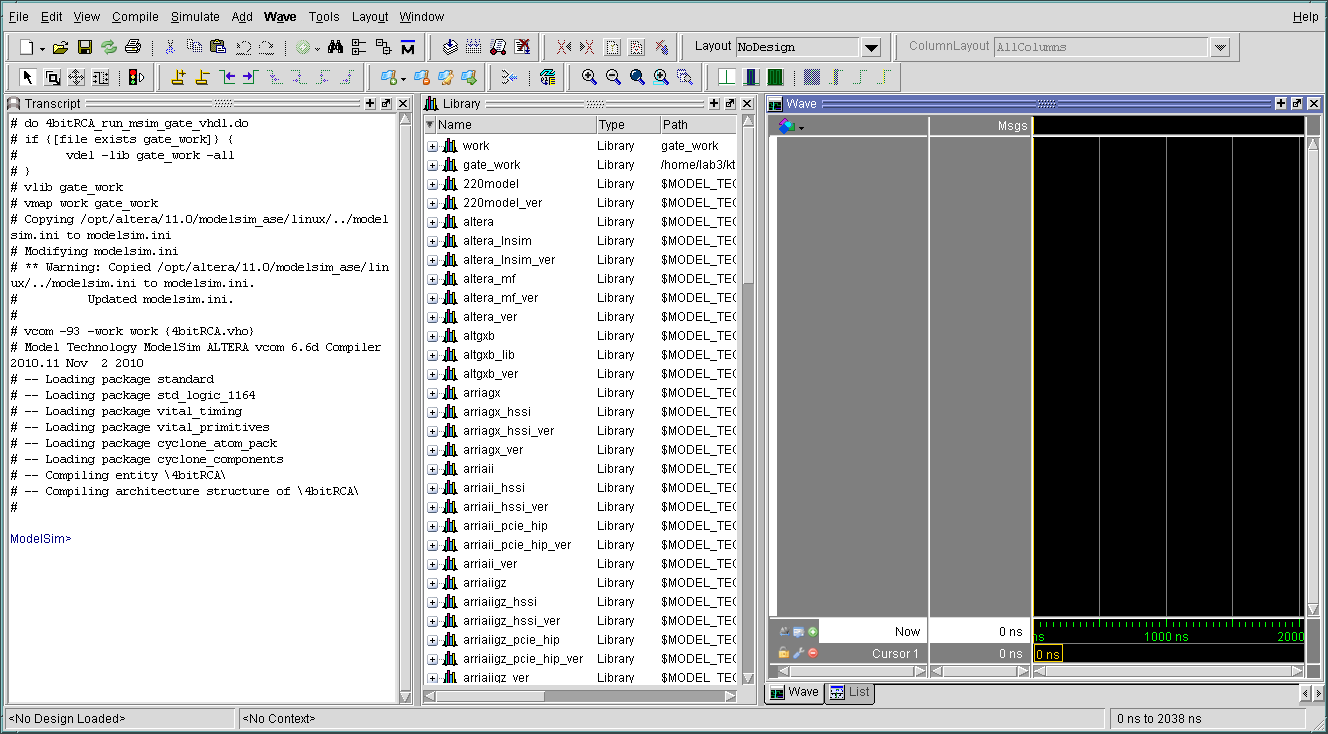

ModelSim起動

Quartus II からシミュレーションツール ModelSim を起動する。

- "Tools" → "Run Simulation Tool" → "EDA Gate Level Simulation.." で起動。

(HDLで書いたモジュールは RTL Simulation も実行可能。)

- "Timing Model" に "Slow Model" を選んで "Run"。

- 別ウィンドウが立ち上がる。設計した回路は "gate_work" にある。"work" は "gate_work" へのリンクになるので中身は同じ。

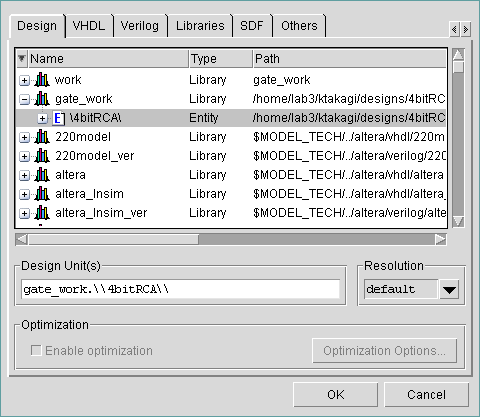

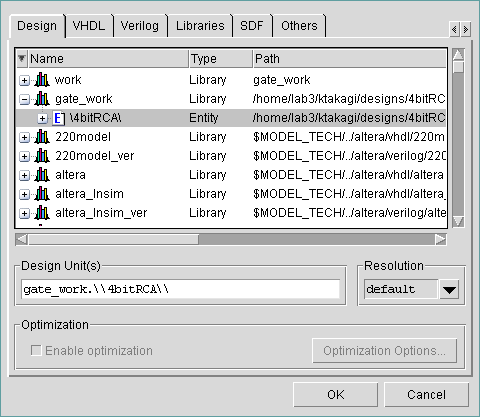

シミュレーション準備

シミュレーションの環境を設定する。

- "Simulate" → "Start Simulation..." で設定ウィンドウを起動。

- "Design" タブの "Design Unit(s)" に "gate_work - (設計したエンティティ)" を選ぶ。

- (Verilog HDL の場合、"Libraries" タブで "Search Libraries" に "Add..." して必要なライブラリ (cyclone_ver、メモリ、Megafunctions) を設定する必要がある。)

- "OK"。

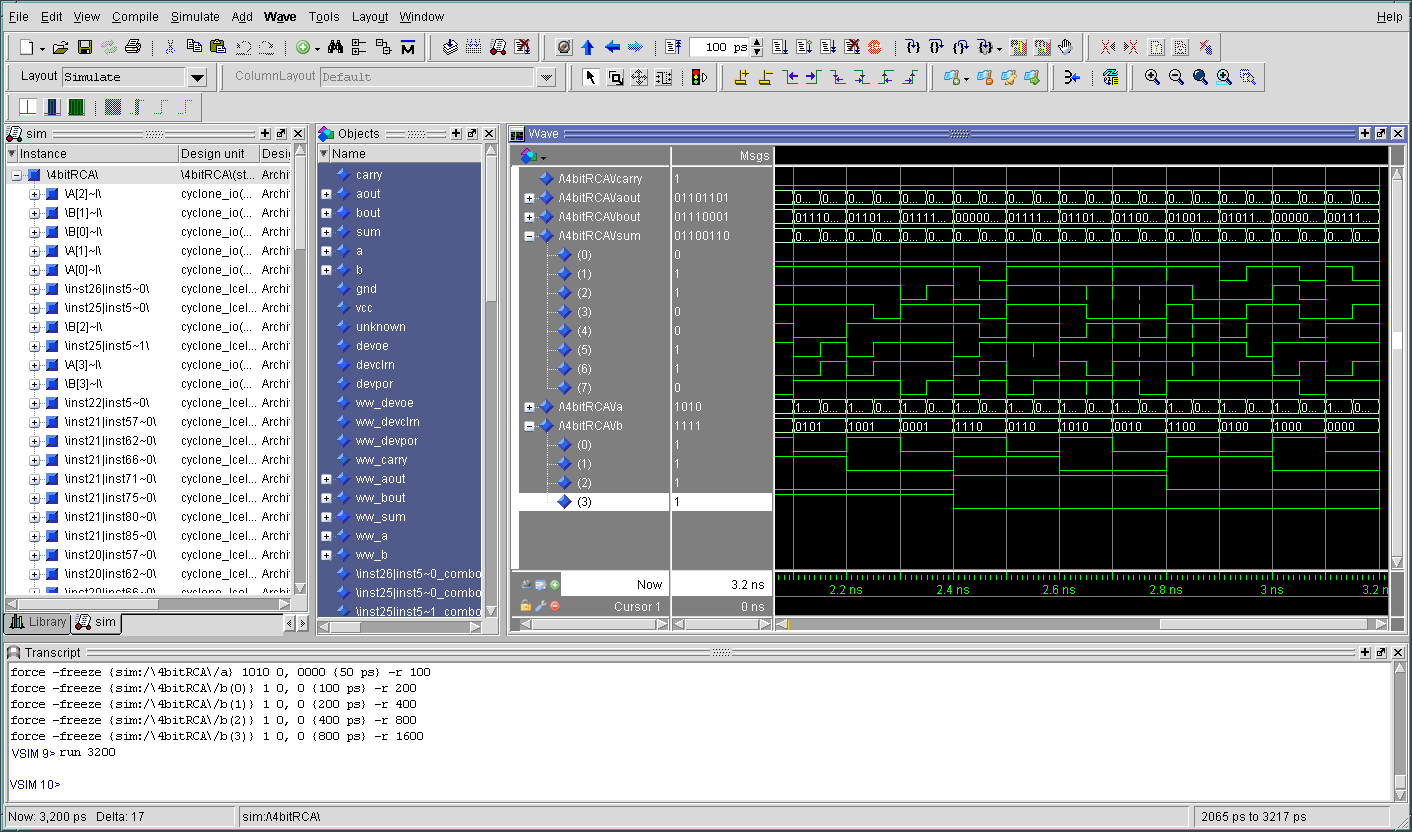

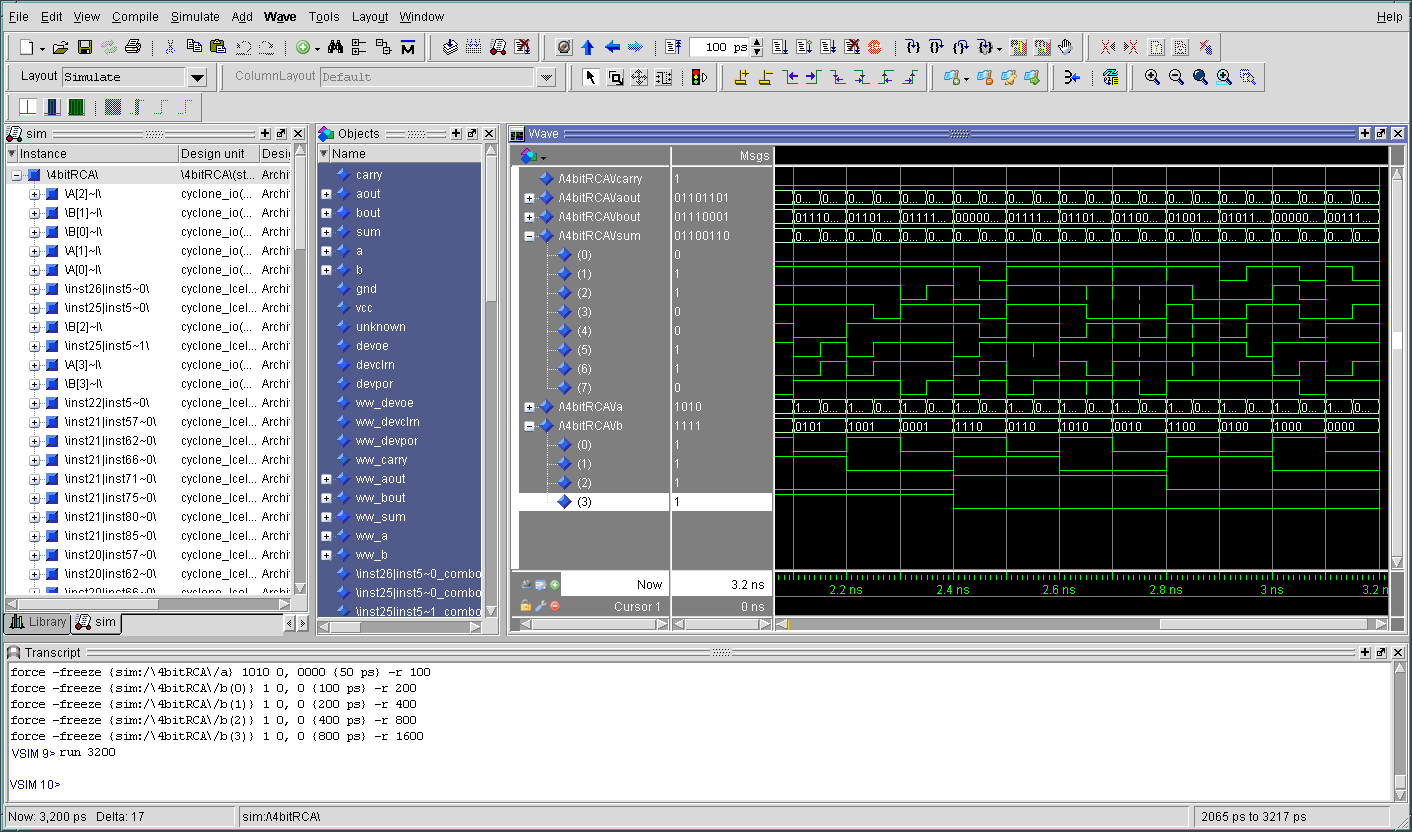

シミュレーション実行

入力波形を与えてシミュレーションする。

- "Objects" サブウィンドウから観測したい信号線を "Wave" サブウィンドウへドラッグする。

- "Wave" サブウィンドウの入力信号線で右クリックメニューから "Force" や "Clock" で値を設定する。

- "Simulate" → "Run 100" などでシミュレーションを実行する。

作業の効率化のヒント

- "Transcript" サブウィンドウに直接コマンドを入力して実行できる。慣れてきたらメニューをクリックするより早い。コマンドヒストリも使える。

- 実行履歴は "./simulation/modelsim/msim_transcript" に残るので、編集して別名で保存しておくとよい。do (ファイル名) で実行する。

- 例: こんな感じでスクリプトを書いておいて実行する。

force -freeze {sim:/\my_design\/clk} 1 0, 0 {50 ps} -r 100

run 5000

-

- 複雑な入力パタンを記述したい場合、HDL で入力波形を書いたテストベンチを用意して、Quartus II の "EDA Tool Settings" - "Simulation" カテゴリで "Compile test bench" に指定するとよい。(新版: テスト波形ファイルを使ったシミュレーション)

Last modified: 2014/4/11 10:00