主記憶用のRAMの作り方

- 本ページの画像は,Quartus 13.1sp1/旧ボードMU200に沿ったものなので,青字としている本文の記載を真として画像は適宜読み替えてください.(参考:v13.1sp1編/旧ボード編)

- 2ポートのRAMを作成した場合,RAMのポートが全て使われるのでQuartusから実機上のRAMを見ることができません.

megafunctionによる主記憶用RAM作成

[注意] compiz が動いていると MegaWizard が固まります.

デスクトップの [システム]→[設定]→[外観の設定] で [視覚効果]タブで「効果なし」に設定して下さい.

MegaWizardの画面表示が小さいと操作の途中で固まります.立ち上げてからまずスクロールバーが消えるくらい画面を大きくすると解消できるようです.不思議です.

FPGA上で大規模な回路を実装する時に,

それらの回路を効率よく実装するため,

FPGAベンダはいくつかの代表的な回路に対して

マクロを準備しています.

主記憶用のRAMは,このマクロ(Alteraではmegafunctionと呼ぶ)を

用いて作成します.

以下では RAM の作り方を説明しますが,他の megafunction も同様に作れます.

なお,通常のRAMはアドレスを与えると即データを出しますが,

Altera FPGAのRAMはレジスタが必ず入り,

アドレスを入力した後にクロックを入れないとデータが出てきません.

注意して下さい.

- メニューから "Tools" → "IP Catalog" を選択する.

- 右側に表示されるIP Catalogメニューから,Library → Basic Functions → On Chip Memory → RAM: 1-PORT を選択

- IP variation file name: を入力してOK

- IP variation file typeはご自由に

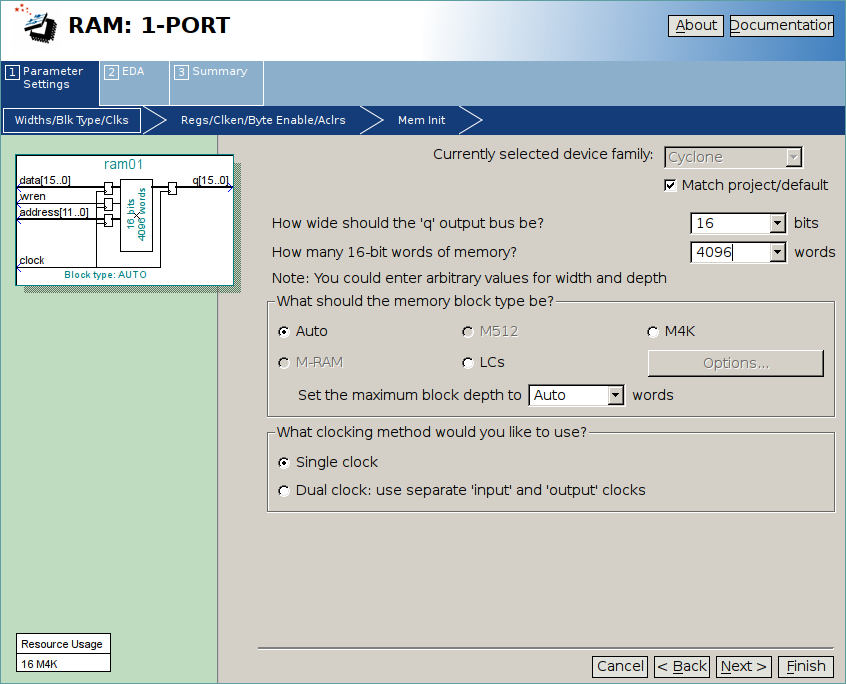

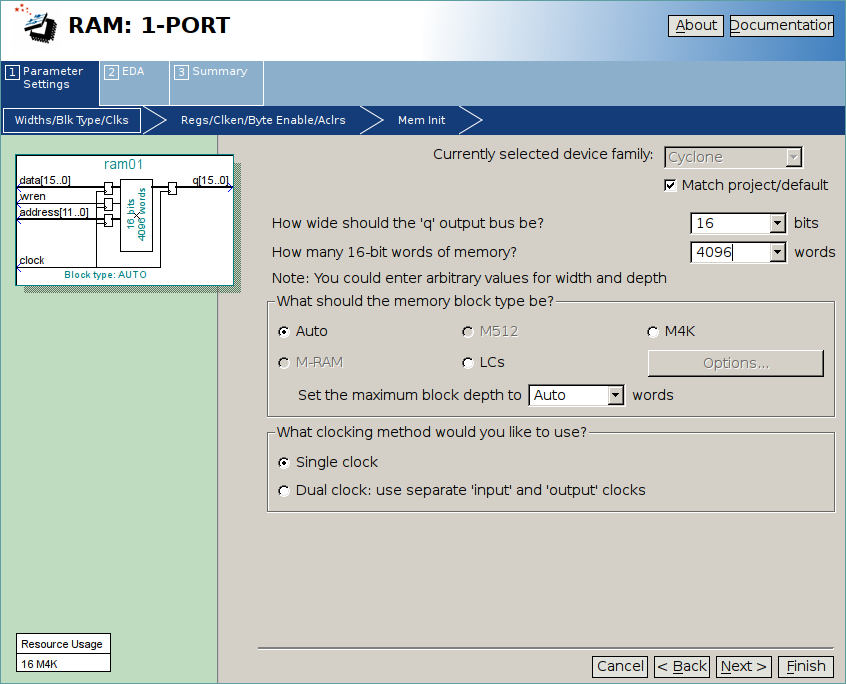

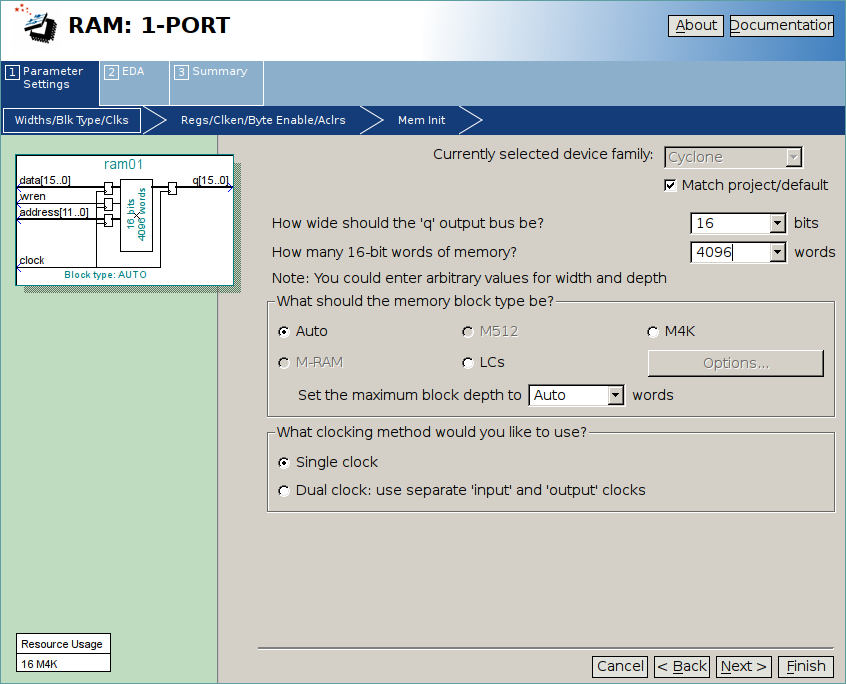

- データビット幅を入力: 16 bits.

- ワード数を入力: 4096 words.

- EP4C30のエンベデッドRAMは540672ビット.最大16 bits x 33792 words.

- SIMPLEの仕様はアドレス空間 64k words だが,FPGA上のRAMが足りないので妥協してよい (ソートプログラムも 4096 words あれば十分)

- メモリの仕様,使い方は,このウィンドウの右上の Documentation からたどれる文書を参照して下さい.

- "Next>".

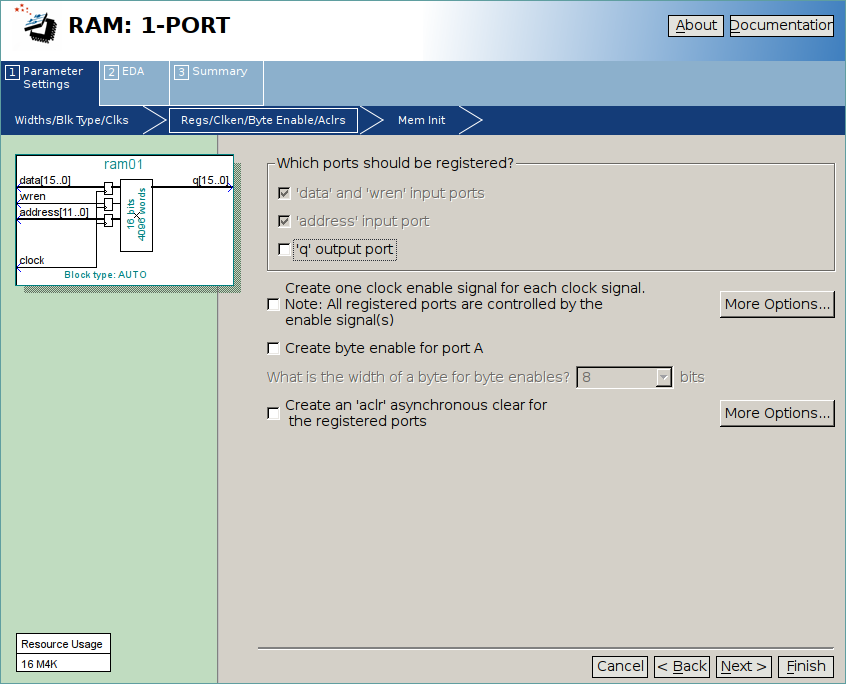

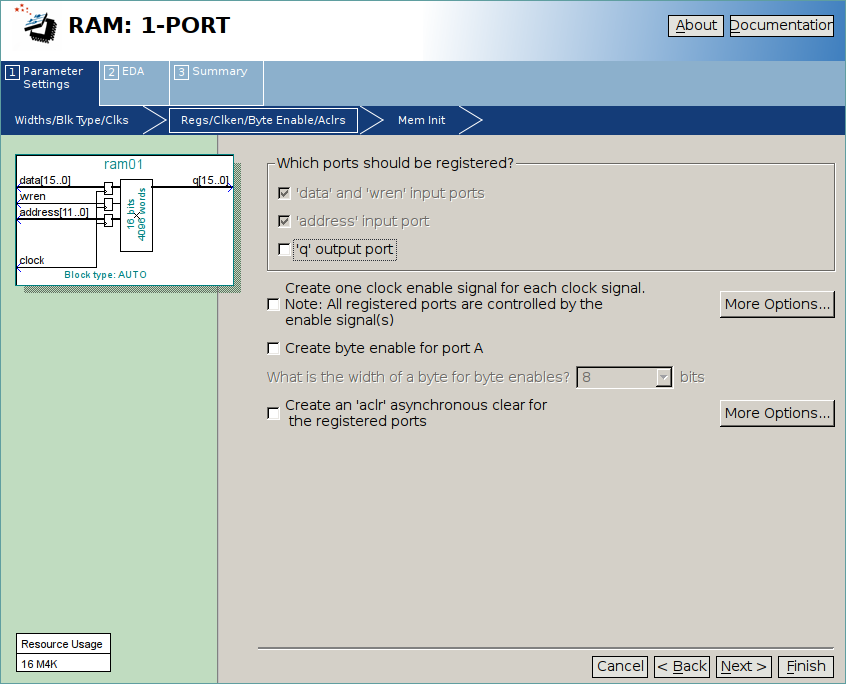

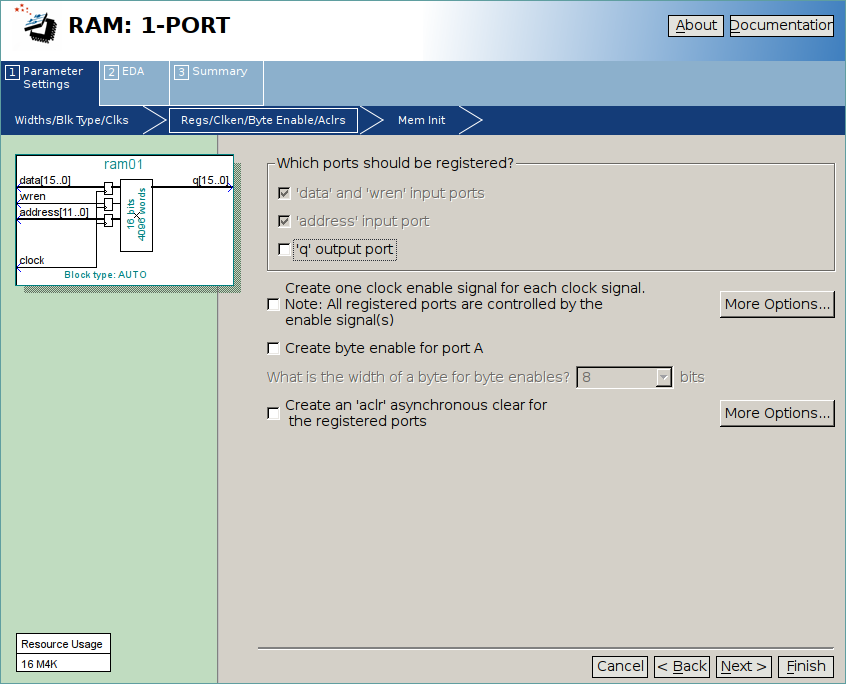

- "Which ports should be registered?" の "'q' output port" を外す.

- "Next>".

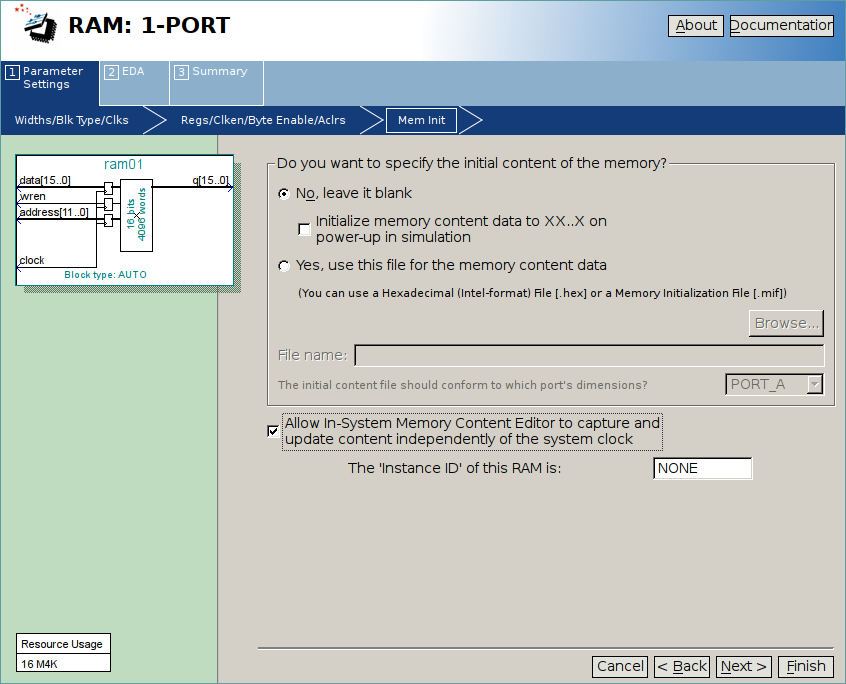

- 次のページはそのまま "Next>".

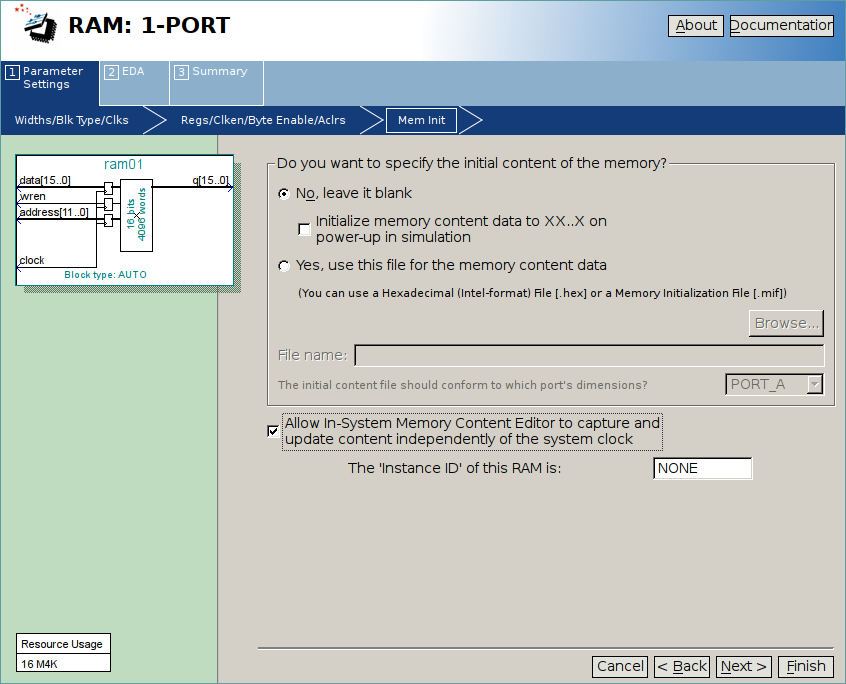

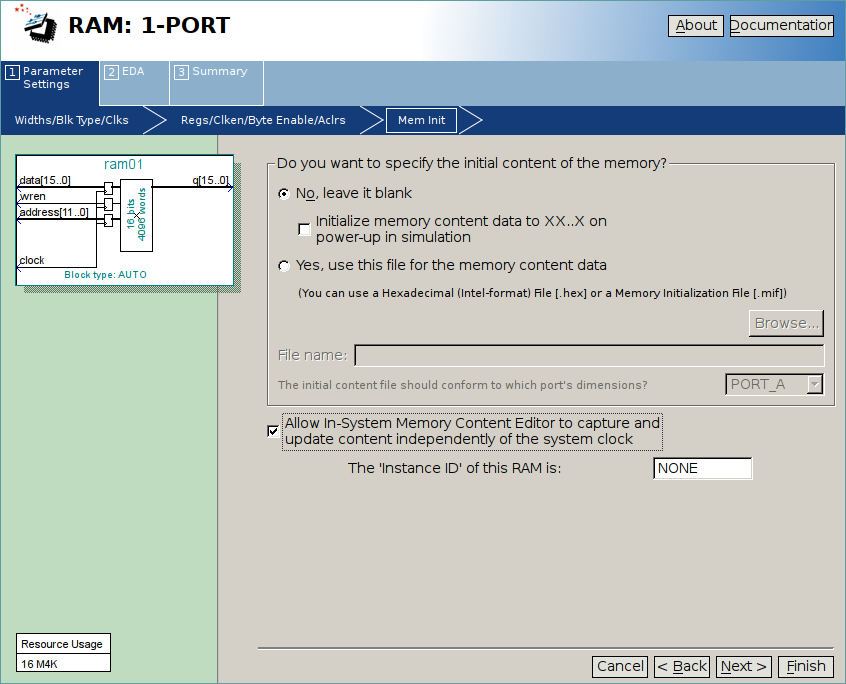

- 動作中の主記憶の様子をIn-System Memory Content Editorで見ることができるようにするため,

"Allow In-System Memmory Content Editor to capture and update content..."をチェックする.

- あらかじめ主記憶に書き込むデータのファイル(ファイルの作り方は後方を参照)を準備してあるなら,

"Do you want to specify the initial content of the memory?"

をYesにし,ファイルを指定する.以後,XXX.v内で指定されているaltsyncram_component.init_fileを変更することで,ファイルを変更することができる.

- "Next>".

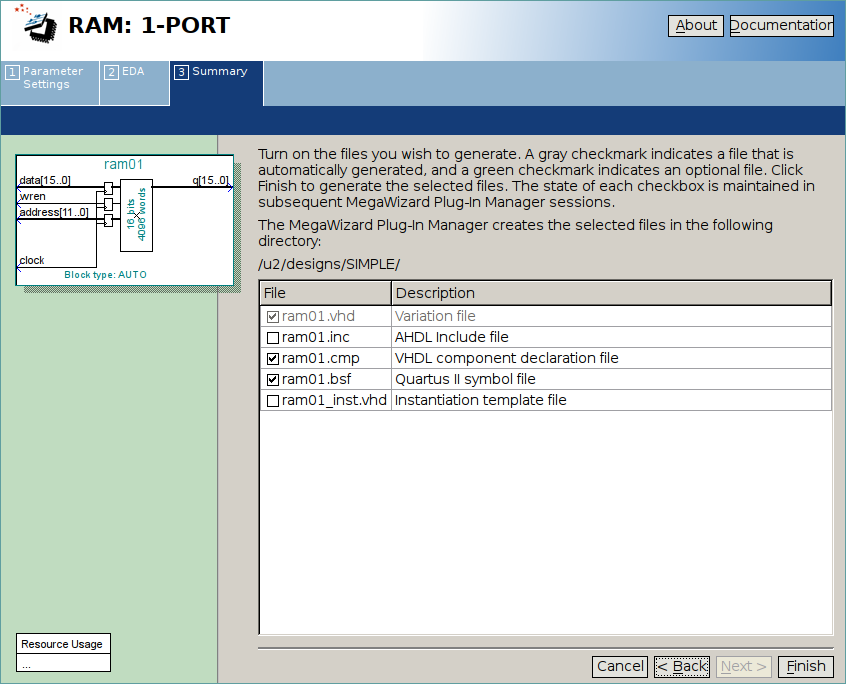

- 次のページはそのまま "Next>".

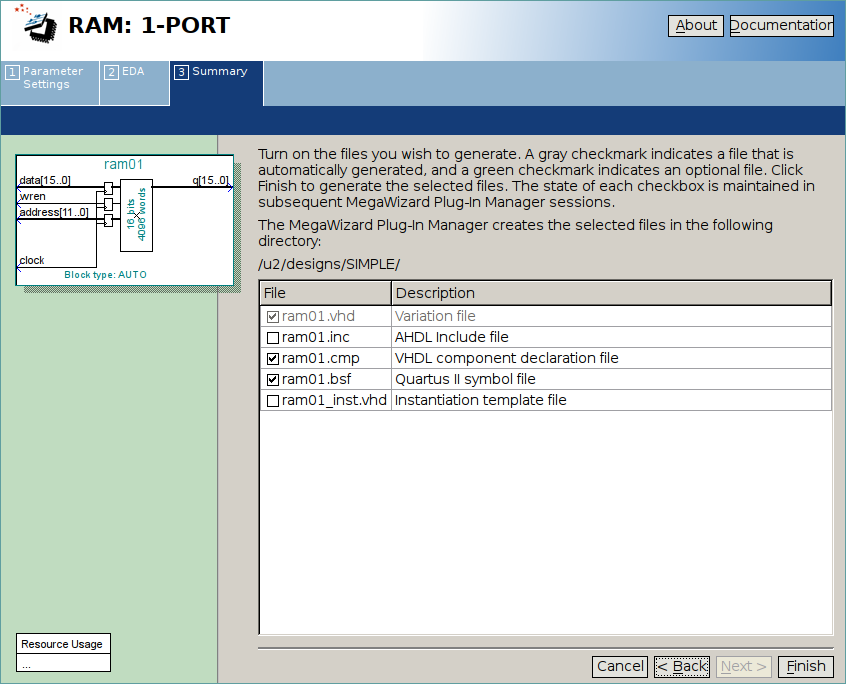

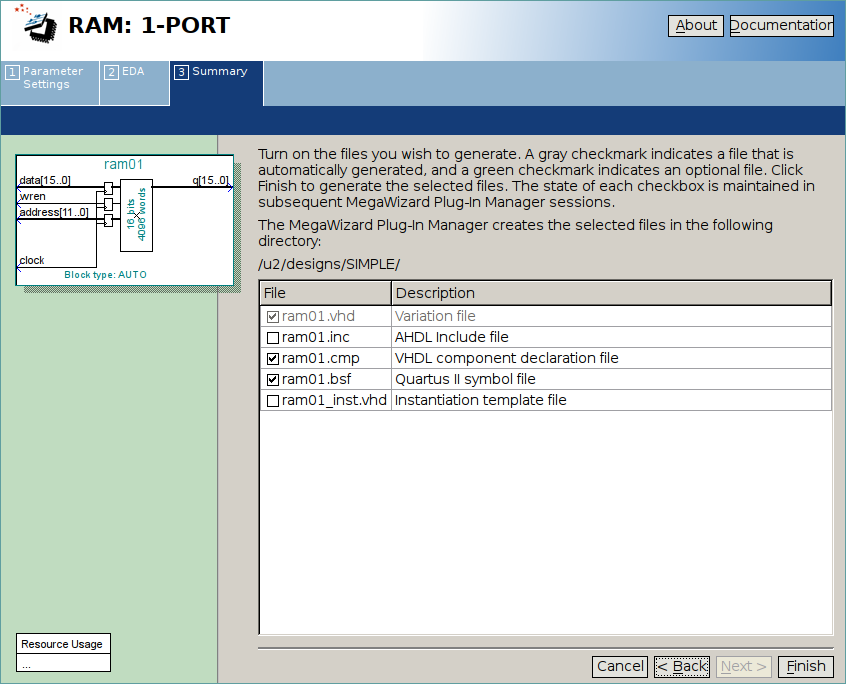

- インスタンス記述のテンプレートファイルを作る場合は,"Instantiation template file" の _inst.v ファイルにチェックを入れる.

- 回路図から呼び出すシンボルを作る場合は,"Quartus II symbol file" の .bsf ファイルにチェックを入れる.(全部HDLで設計する場合は不要)

- XXX_bb.v(Verilog HDL black-box file)は不要

- "Finish".

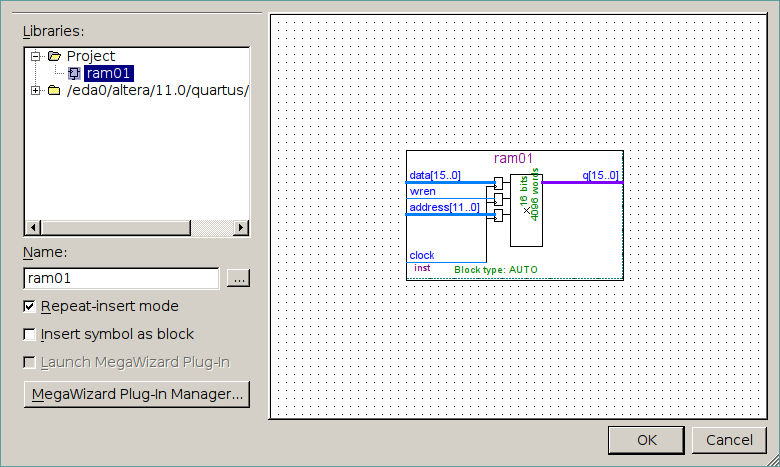

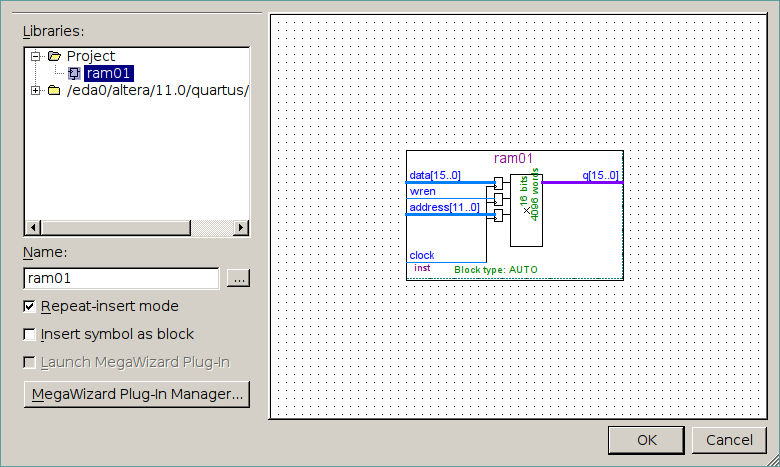

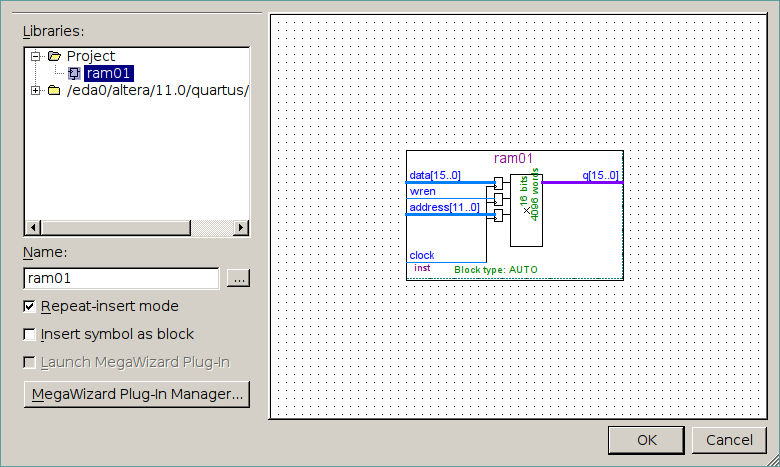

- Symbol Tool の自分のプロジェクトの下にメモリができているので,回路図上に配置するか,HDLのサブモジュールとして接続する.

- wren は WRite ENable の信号です.1にしたときにRAMにデータを書き込めます.

- 直接 lpm_ram_dq を呼び出してパラメータを個別に設定しても,できるものは同じです.

主記憶(RAM)のデータ・ファイル(プログラムも含む)の作り方

- "File→New→Memory Files→Memory Initialization File"を選択し,

メモリ・ファイル・エディタを立ち上げる.

- ワード数とワード・サイズを聞かれるので,

ワード数には必要なワード数を指定し,ワード・サイズを16を指定する.

- Excel風のウィンドウが出ますので,RAMの内容を編集します.

保存すると,拡張子が.mifのMemory

Initialization File(MIFファイル)が作成されます.

- "View→Cells Per Row"で1行あたりのワード数を変更できるので,

使いやすいワード数にすると良いでしょう.

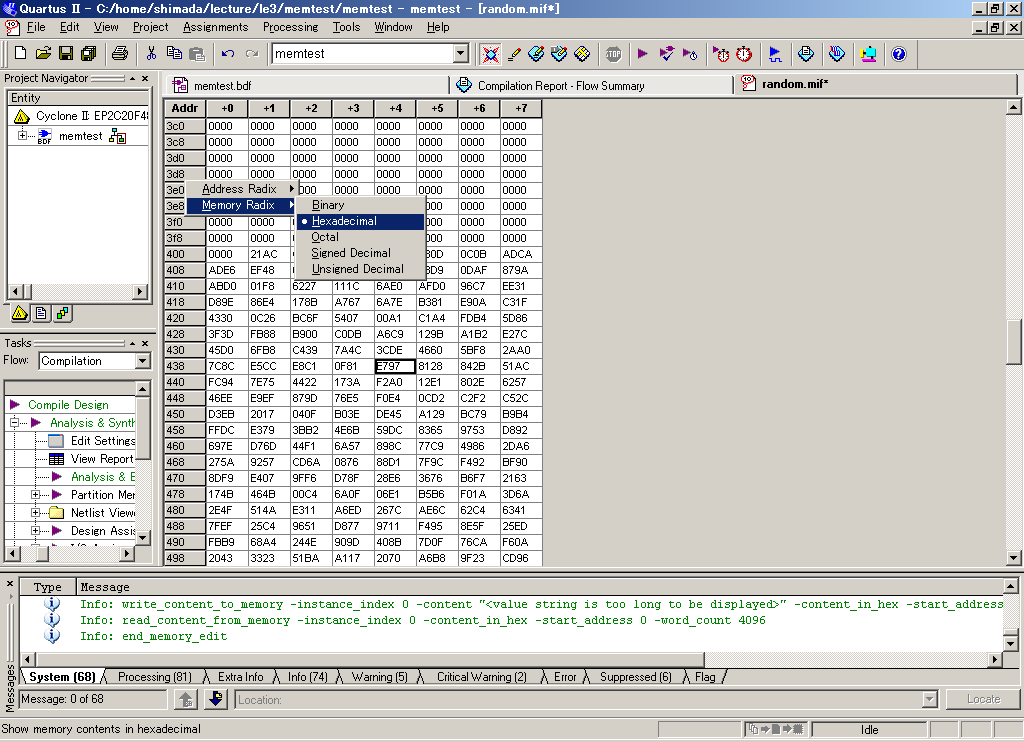

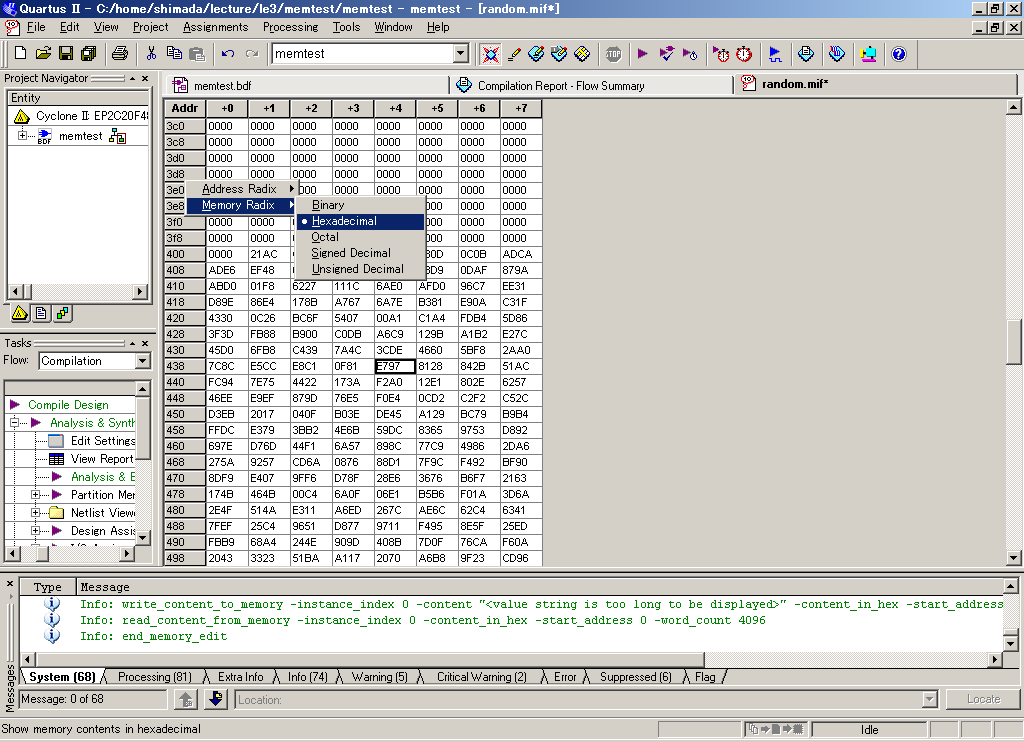

- "View→Adress Radix"および"View→Memory Radix"で

表記(2進数/8進数/10進数/16進数)を変えれるので,

好きな表記で編集すると良いでしょう.

- セルの間に新たなセルをいれたければ,"右クリック→

Incert Cell"で間に新たなセルを挿入できます.

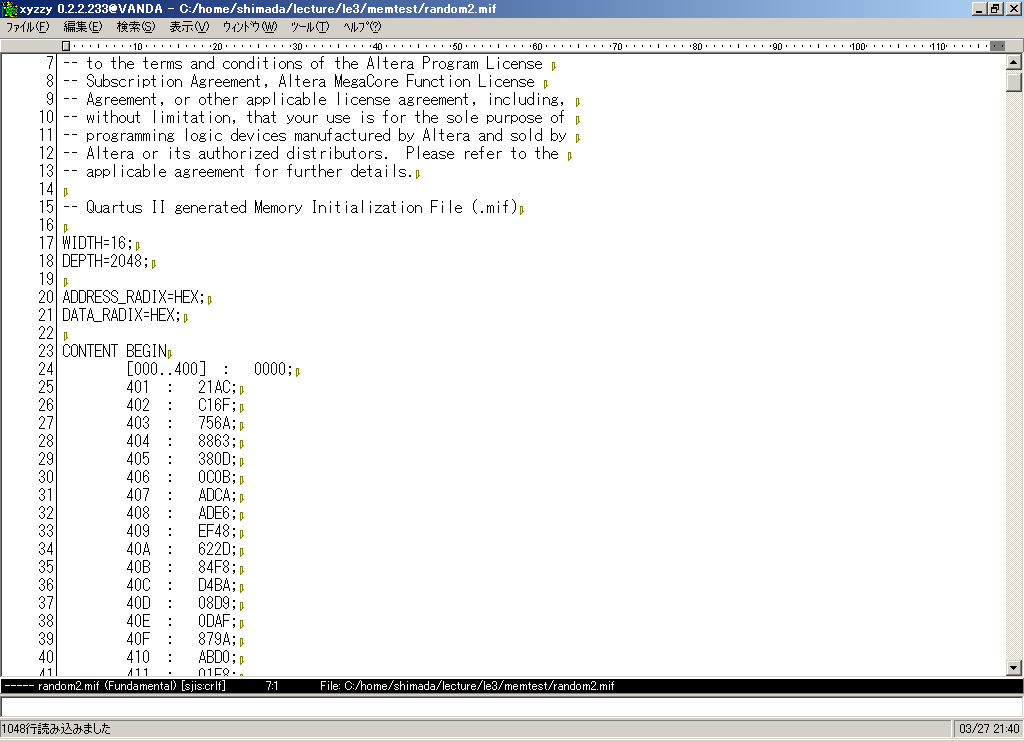

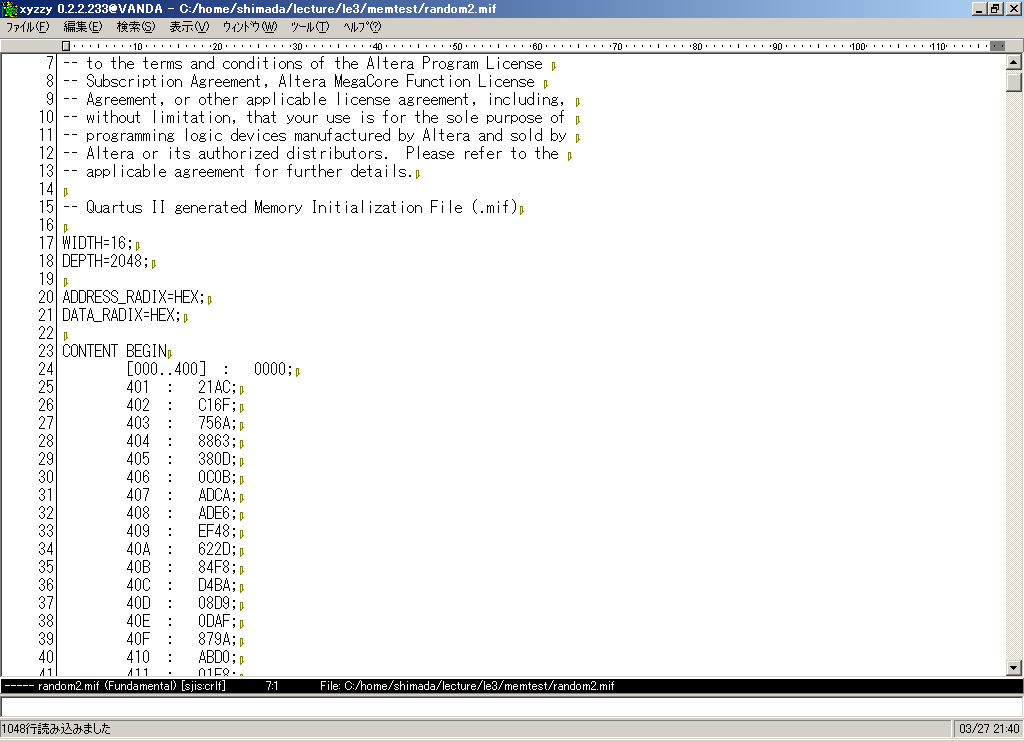

- MIFファイルは簡単な構造のテキスト・ファイルですので,

直接いじくることも可能です.

- アセンブラを作るのでしたら,この形式で出力させるように作ると良いでしょう

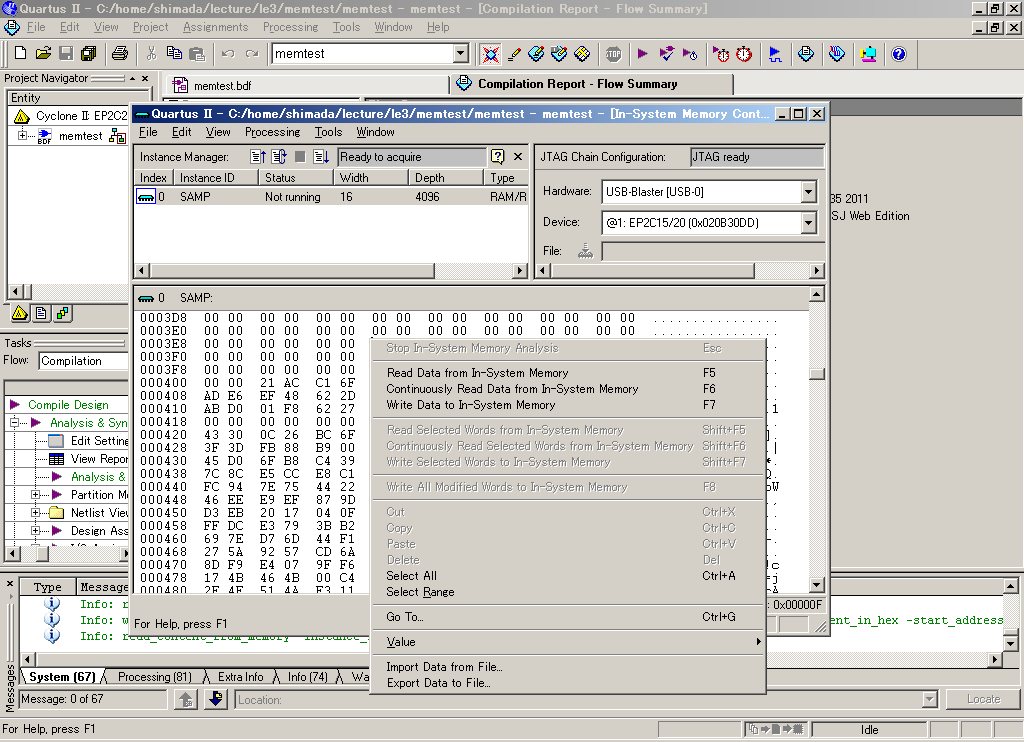

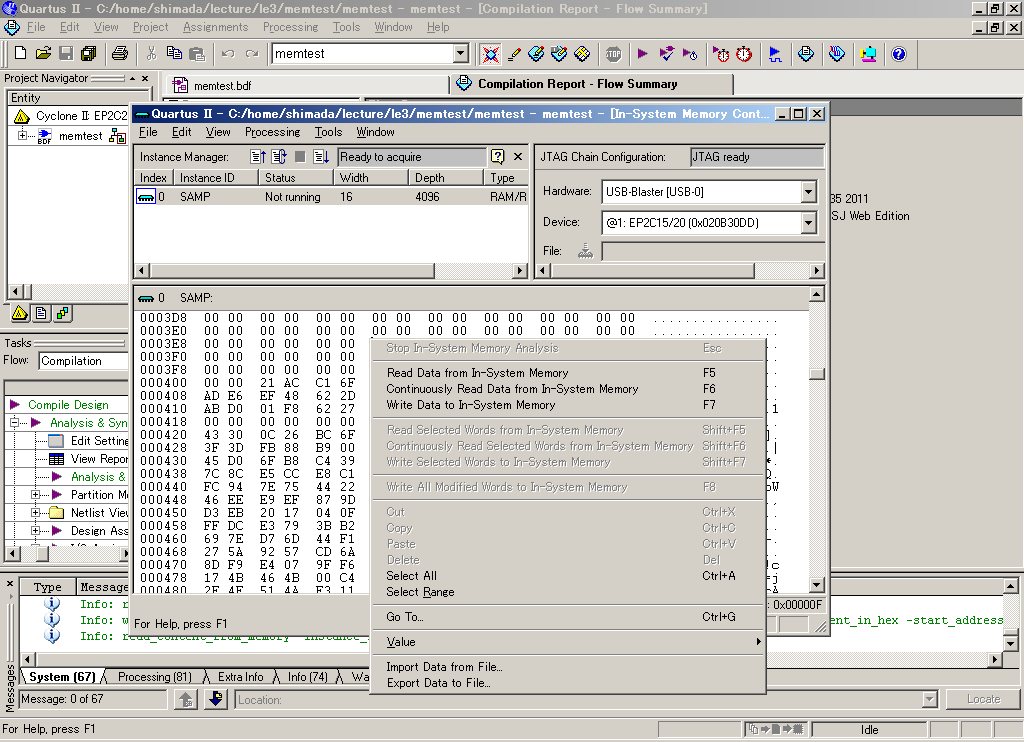

FPGAで動作中の主記憶(RAM)を読み書きする

QuartusIIに付属するIn-System Memory Content Editorを

使うことにより,FPGAで動作中のRAMの内容を見たり操作することができます.

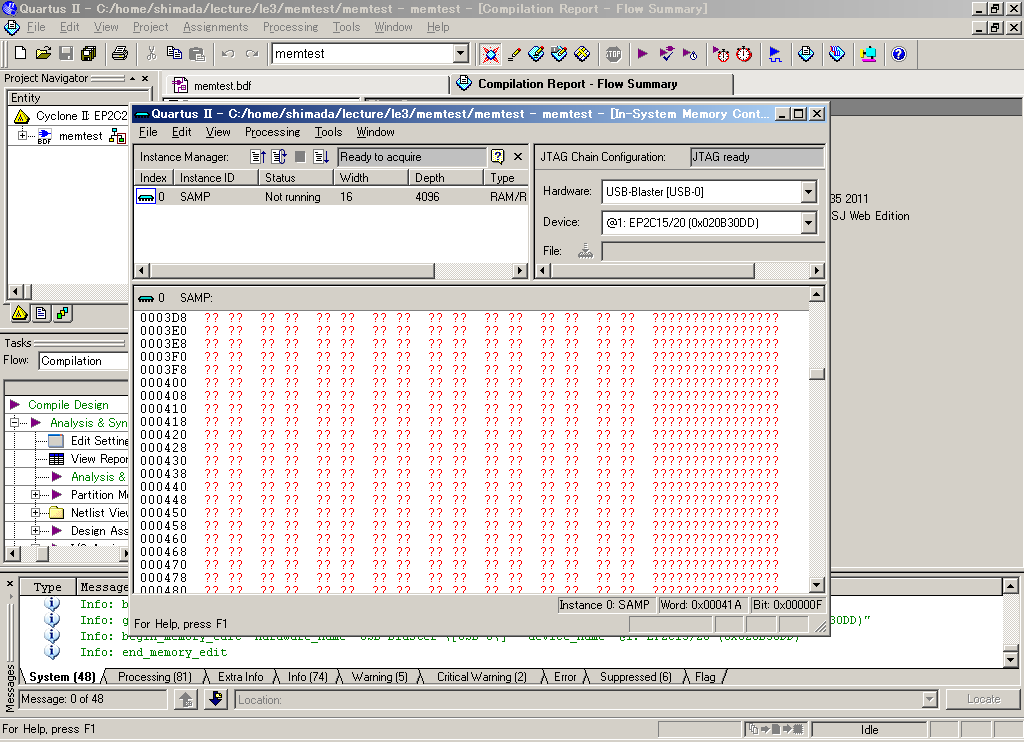

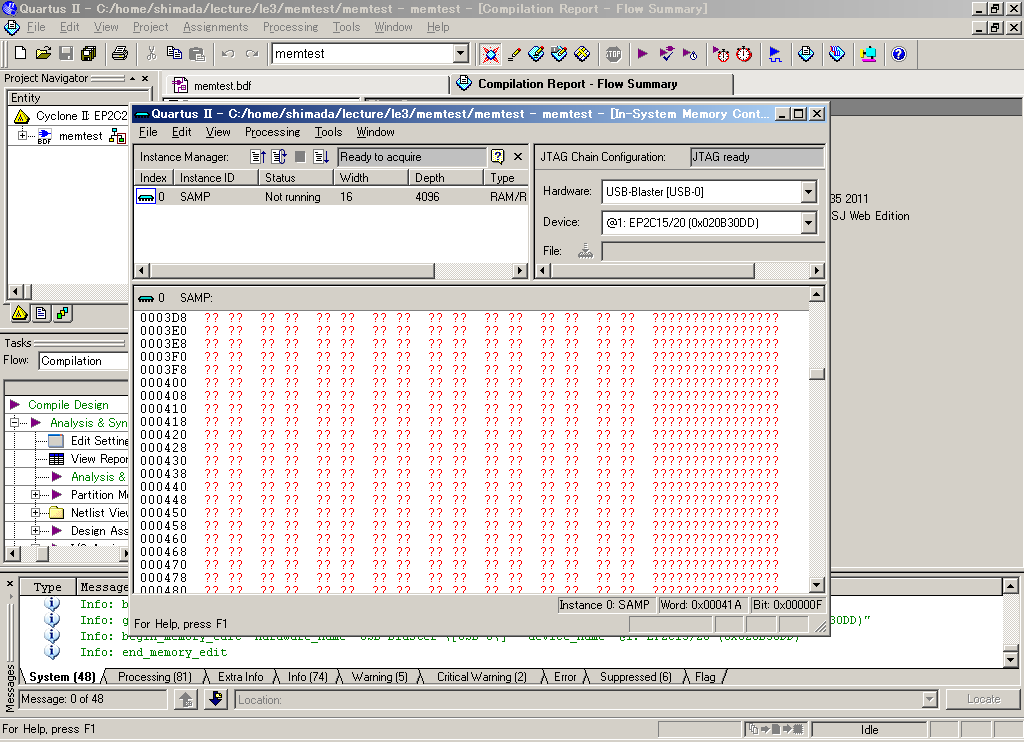

- "Tools→In-System Memory Content Editor"を立ち上げます.

- 右上の"Hardware"の項目で"USB-Blaster"を選択します.

- 問題がなければ,左上の"Instance Managaer"にFPGA中に作成

されたRAMの一覧が出ます.

- "Instance Manager"でエディットするRAMを選択します.

- 下のRAMの内容を示すウィンドウが"??"で埋まります.

- 下のRAM内容を示すウィンドウでRAMの操作を行います.

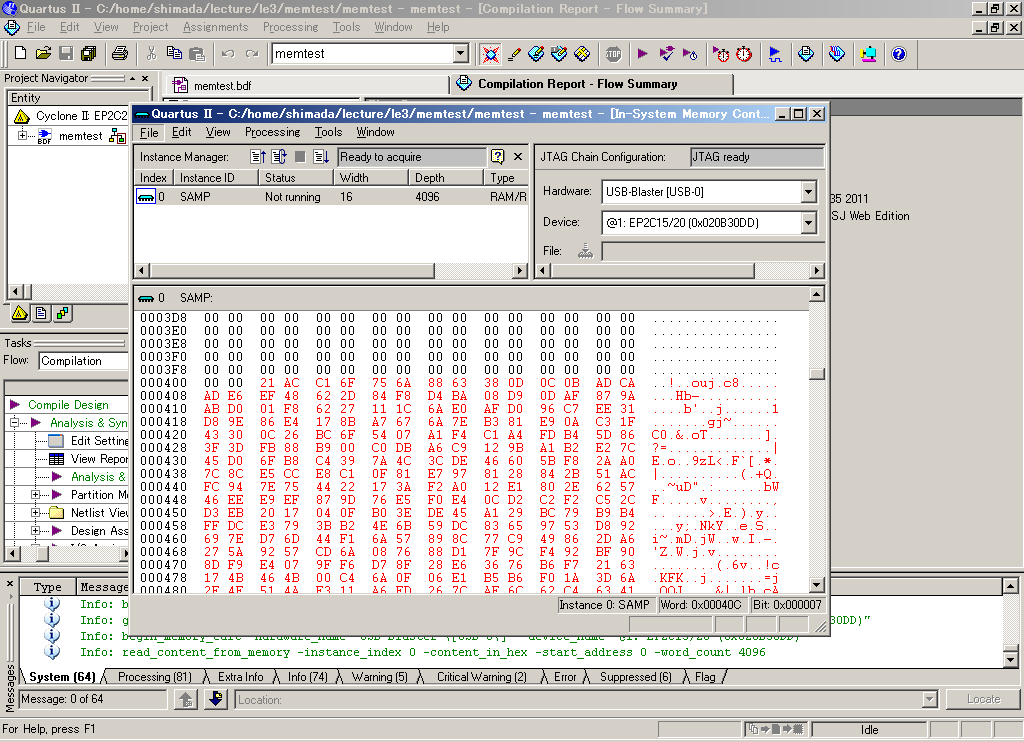

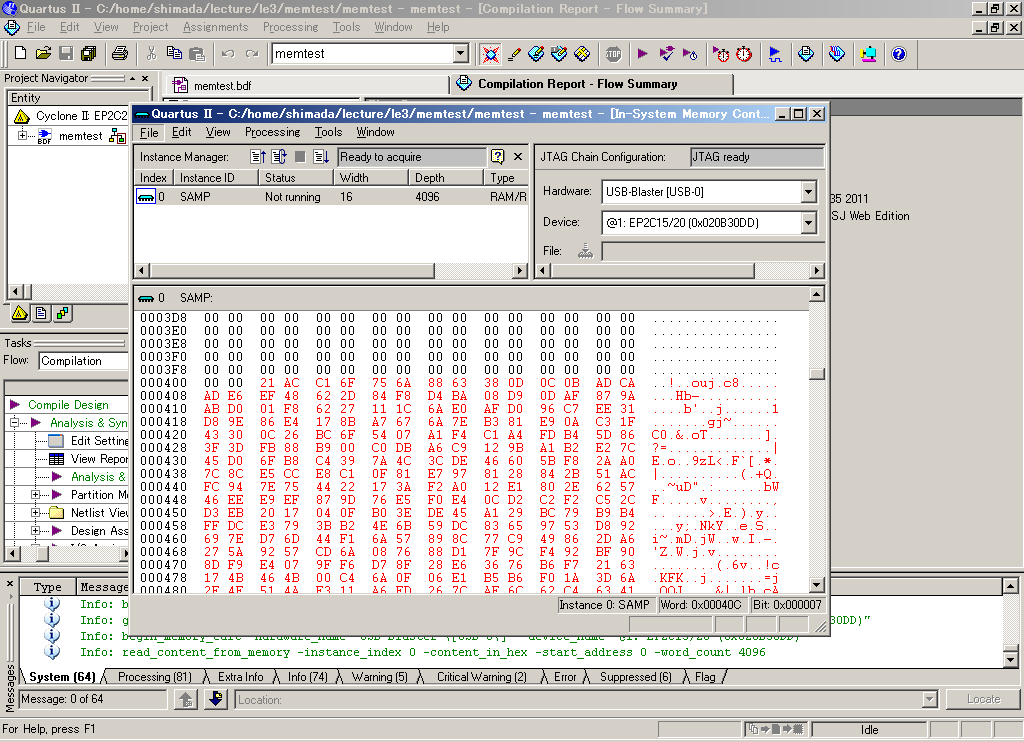

- ウィンドウを右クリックして"Read Data from In-System Memory"を

選択すると,RAMの内容を読み込みます.

- (前回の読み込みから)更新された部分は赤色で表示されます.

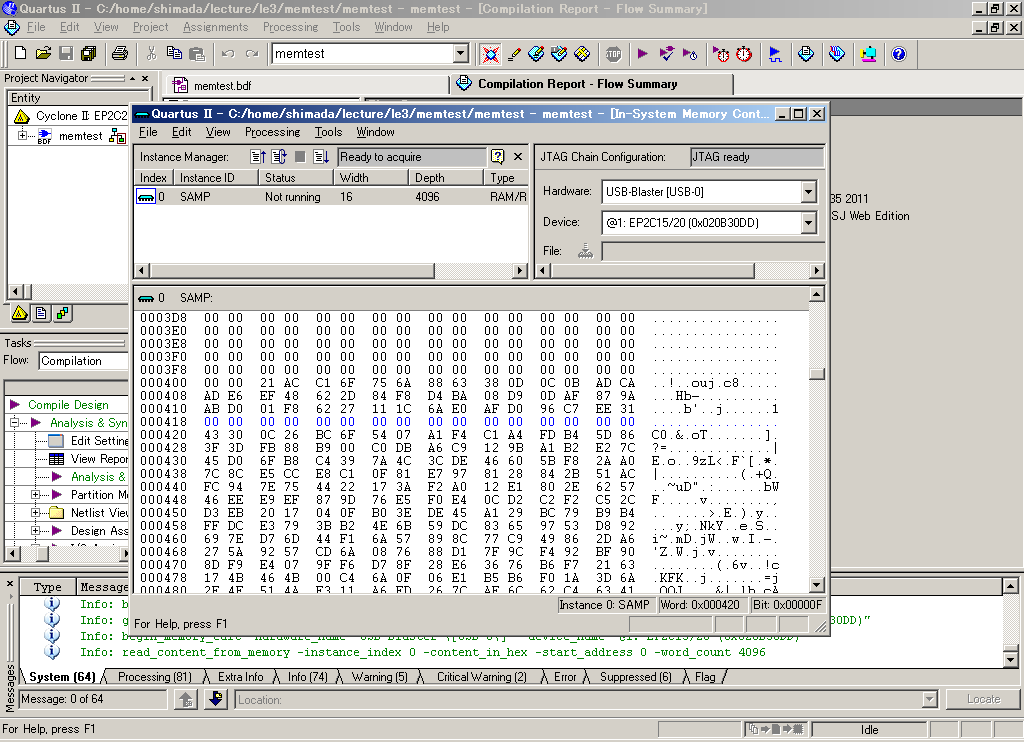

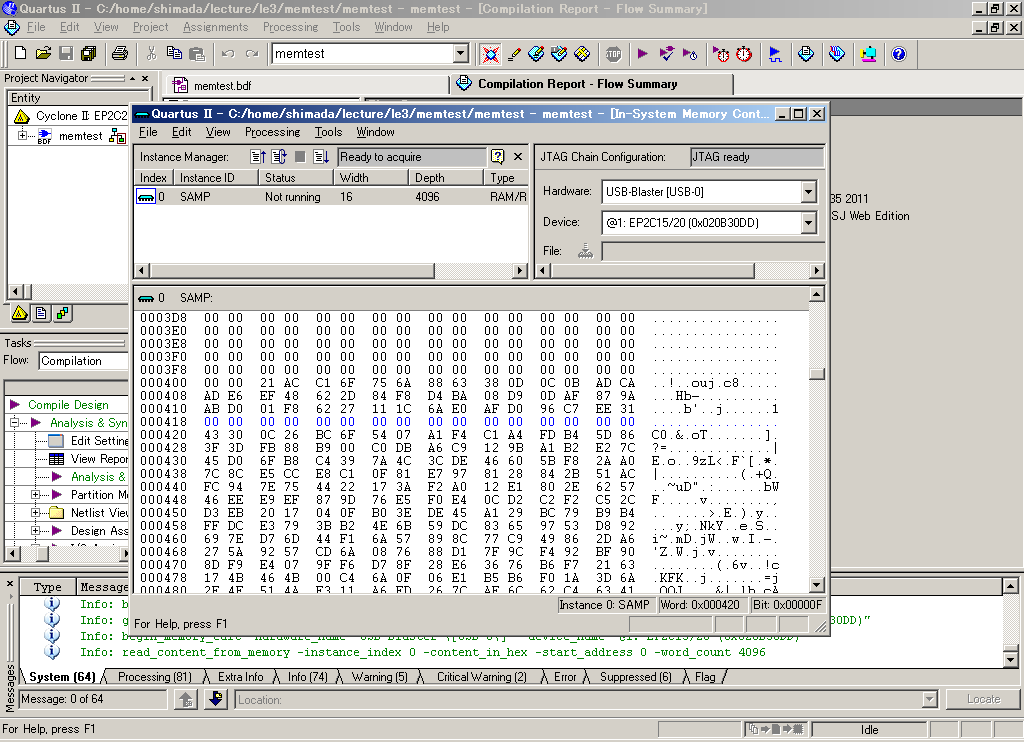

- RAMの内容の変更のしかた.

- 変更したい部分の左にカーソルと持って来て,

書き込みたい値を入力します.

- 書き込まれた値は青色で表示されます.

- この時点では,変更はまだFPGA内部には反映されていません.

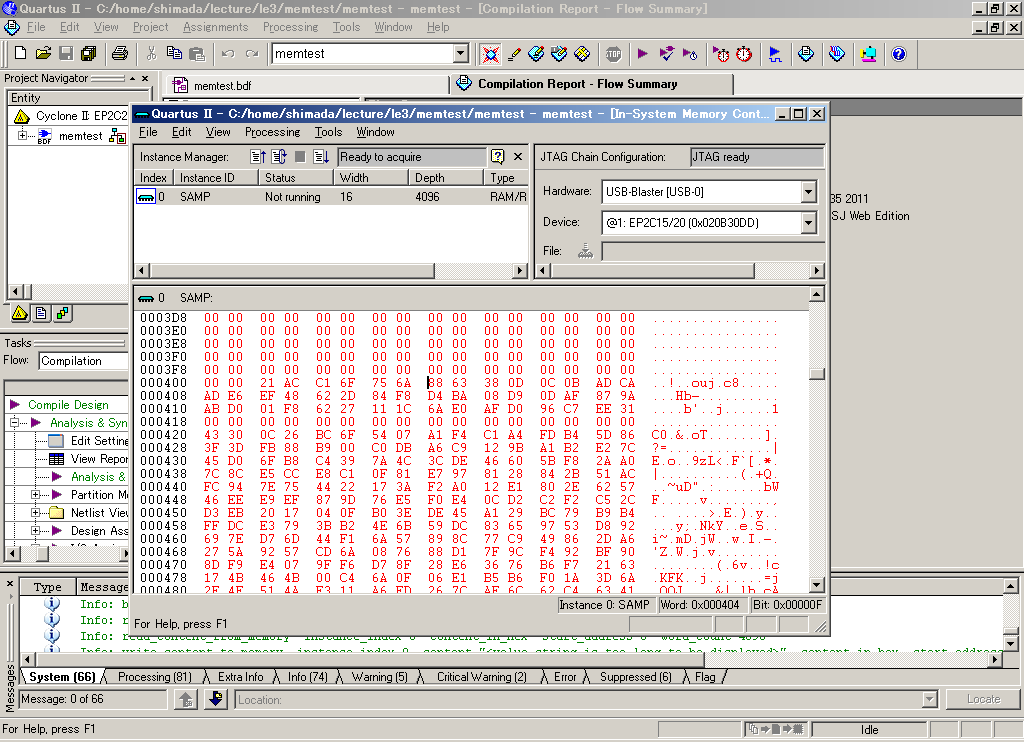

- ウィンドウを右クリックして"Write All Modified Words to

In-System Memory"を押して経ん後部をFPGAに書き込みます.

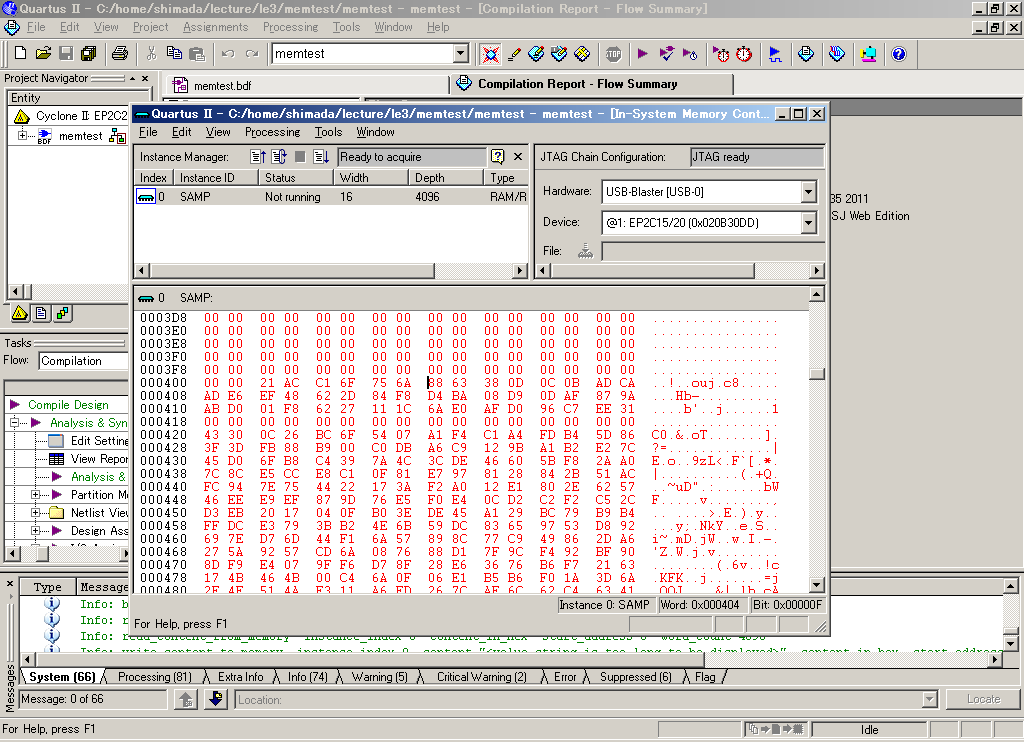

- ウィンドウを右クリックして"Continuously Read Data from

In-System Memoery"を選択すると,

RAMの内容を0.5秒ぐらいの間隔で読み込みを繰り返します.

- リアルタイムでRAMが更新されている様子が見えます.

- 更新された部分は,一瞬,赤色になります.

- ウィンドウを右クリックして"Stop In-System Memory Analysis"を

選択すると,リアルタイムの更新を終了します.

- メモリ・アクセスまわりのデバッグを行う場合は,

クロック周波数1Hzぐらいで動作させながら,

RAMの内容を見ると良いでしょう.

- 他にも,右クリック後の操作で書き込む値をMIFファイルから

読み込んだり(Import Data from File),

逆に,メモリの内容をMIFファイルに書き込んだり

できますので(Export Data to File),必要に応じて利用してください.

In-System Memory Content Editorの詳細は,

Quartus IIハンドブックのVolume 3, Chapter 15, "FPGAメモリおよび定数のインシステム・アップデート"に書かれています.